| News | 2001年4月18日 11:00 PM 更新 |

Intelチップの電力密度は“原子炉レベル”?

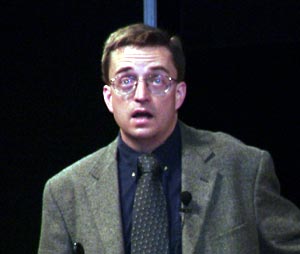

IDFの基調講演に登場したIntelのPat Gelsinger氏は,CPUの高性能化に伴い,電力消費の増大が大きな課題になったと指摘する。Pentiumがホットプレートレベルなら,今のチップは原子炉レベルなのだそうだ。

「Intel Developer Forum 2001 JAPAN」(IDF)の2日目となる18日,基調講演を担当したのは,米Intel副社長兼CTOのPat Gelsinger氏だ。R&Dの最高責任者である同氏は,世界各地のインテルラボが開発を進めている4分野の技術を紹介するとともに,プロセッサの発熱量に関する警告を発した。

同社が注力する4つの分野とは,シリコン技術,プラットフォーム・アーキテクチャ,コミュニケーション,そしてインターネット技術。世界経済が先行き不透明感に支配される中で,同社は今年1年間で75億ドルの設備投資と42億ドルの研究開発予算を計上している。

シリコン技術としてGelsinger氏が取り上げたのは,1ボルト以下の動作電圧で10GHzを実現するプロセッサだ(3月9日の記事を参照)。約20億のトランジスタを集積しながら,わずか40ミリ四方というダイサイズになるという。「このシリコン酸化膜のゲート長は,およそ30nmだ。物理法則を超えると言われていた技術が,6〜8年後には実現する。これは大いなる進歩だ」(Gelsinger氏)。これにより,「ムーアの法則」は今後10年間,守られるという。

しかし一方で同氏は,CPUの高性能化に伴い,電力消費の増大が大きな課題になったと指摘する。これは,2月の国際固体素子回路学会(ISSCC)でやはりGelsinger氏が語った内容とほぼ同じ(2月6日の記事を参照)。現在のCPUは,表面の1平方センチあたりに換算すると100ワットを超える電力密度となり,これは「原子炉に近い数字だ」という。「Pentiumの頃はホットプレートのレベルだったが,このままいけば,10年後には太陽の表面と同じレベルの密度になるだろう。特に,PCの小型化傾向の強い日本においては重要な問題だ」(Gelsinger氏)。

冷却装置に対する要求はより厳しくなり,また縮小化が進むきょう体を含んだプラットフォームレベルの冷却対策も必須となる。「過去,ムーアの法則を制約していたのは製造性だったが,これからは電力も制約要素になる」(Gelsinger氏)。今後は,熱放散の新しい手法を開発する一方,マイクロアーキテクチャでもCPUのマルチスレッド化や複数コアのオンダイ化などを通じて実行効率の向上を図るという。

|

| ゲルシンガー氏が持っているのは,2002年に実用化される12インチウェハー。「まるでピザのよう」(同氏)なこの大径ウェハーがPentium 4の製造コスト削減を担う。インテルは,2010年から2015年にかけて,さらに大きな18インチウェハーを導入する予定だ |

関連記事

![]() 10GHzにまた一歩近づいたIntel

10GHzにまた一歩近づいたIntel

![]() 今後のチップ設計の課題「熱」に取り組むIntel

今後のチップ設計の課題「熱」に取り組むIntel

![]() 10GHzのチップも夢ではない。チップ各社が語る最先端の取り組み

10GHzのチップも夢ではない。チップ各社が語る最先端の取り組み

![]() チップメーカー,10GHz実現に向けて一歩前進

チップメーカー,10GHz実現に向けて一歩前進

Copyright © ITmedia, Inc. All Rights Reserved.