| News | 2001年6月12日 06:43 PM 更新 |

Intelフェロー,「20GHzプロセッサ」への道を語る(2)

同博士は京都で開かれた「Silicon Nanoelectronics Workshop」でIBM側の開発者と話し合う機会を持ったそうだが,「現状の技術でムーアの法則を実証していく上で,基本的な障害が何もないことを,IBM側には納得してもらった」。

IBMのストレインド・シリコンについて同博士は,「同社が10年以上やっていることは知っている。だが,まだNMOSベースの技術でしかない。PMOSには使えないようだ」と述べ,自社技術の方に汎用性があることを強調している。

ブレークスルーは「プロセス上の工夫」?

実際,今回の20ナノのトランジスタ開発にあたってどんな技術的ブレークスルーがあったのか尋ねても,「プロセス上の工夫」という答えしか返ってこなかった。これはむしろ驚くべきことだ。

例えば,今回の試作で使われた酸化膜は二酸化珪素(SiO2)薄膜であり,リソグラフィプロセスは240ナノメートル――つまり,先端ではあるが,現時点で実用化されている以上の技術ではない。ウエハーは12インチを使用しているが,これは当然のことだろう。

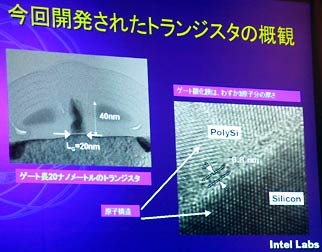

既存のテクノロジーで限界的な小ささ・薄さに挑戦した場合,ショートチャネル効果という電気的クロストークが発生し,この電気的な干渉によってトランジスタが正常に機能しなかったり,「ボロンの突き抜け」と言って,ゲートの電極として用いるポリシリコン中のボロンが,プロセスの熱処理中に絶縁膜を通過して基板の表面濃度を変化させ,しきい値電圧の制御ができなくなる問題が発生することが知られている。

それゆえにこそ,既存のシリコンに代わる技術や,新しい薄膜材料などの研究が進められてきた。しかし,今回のIntelのトランジスタは,そうした代替技術を一切使わずに実現されている。

もちろん,これは「使わない」という意味ではない。例えば酸化膜では「Higk Kのゲート絶縁材料を使うことを検討して」おり,こうした材料を使えば,より薄膜を厚くしてゲートのリーク電流を減らすことができる。露光技術も157ナノメートルやEUV(超紫外線)の利用を同社では研究中だ。

「ゲート長30ナノメートルのトランジスタを0.065プロセス技術で製造する『P1264』というプロセスを2005年に導入予定だが,このあたりから13ナノメートルのEUV技術を使うことになるのではないか」(Chau博士)

だが,既存の技術をベースに20ナノメートルが実現できると実証できたことで,「(なんらかのブレークスルーがなくても)2010年まではムーアの法則を推進することが可能だと証明できた」(同)。同社では今回の開発をフィジビリティ・スタディと位置付けており,今後はイールド(歩留まり)を上げるための研究など,適切な量産に向けたステージに入っていく。単なる研究所の成果発表ではない,実際の製造までを見据えたトランジスタ開発であったことに,今回の“すごさ”がある。

基本的な問題がなかったことで,大まかな道筋は見えた。後はその周辺的な課題の解決になる。「例えば,熱処理などが最も大きい問題。トランジスタの低消費電力化もそのひとつだが,ほかでどう吸収していくのか,ということもある。そのためのパッケージングの研究もアリゾナで進めている」