「Sandy Bridge」のCPUコアが“整然と”並ぶ理由とは:Intel Developer Forum 2010(1/3 ページ)

米Intelが主催する開発者カンファレンス「Intel Developer Forum 2010」(IDF 2010)が米国はカリフォルニア州サンフランシスコで9月13日(現地時間)より3日間の日程でスタートした。初日には米Intel社長 兼 CEOのポール・オッテリーニ氏による近況の総括と、米Intel Architecture Group(IAG)担当ジェネラルマネージャーのダディ・パルムッター氏による「Sandy Bridge」のプラットフォームプレビューが行われた。

IDF 2010の第一報は、このSandy Bridgeにフォーカスして、明らかになった概要を紹介する。

主役はやっぱり「Sandy Bridge」

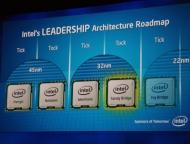

IntelのCPU開発スケジュールセオリー「Tick Tock」でいうと、2010年はアーキテクチャ改良の「Tock」にあたる。Nehalemから新アーキテクチャ「Sandy Bridge」へ進化し、2011年の後半にはプロセスルールを22ナノメートルに進めたSandy Bridgeベースの「Ivy Bridge」が登場する

IntelのCPU開発スケジュールセオリー「Tick Tock」でいうと、2010年はアーキテクチャ改良の「Tock」にあたる。Nehalemから新アーキテクチャ「Sandy Bridge」へ進化し、2011年の後半にはプロセスルールを22ナノメートルに進めたSandy Bridgeベースの「Ivy Bridge」が登場するここ数年のIntelは、「Tick Tock」モデルと呼ぶCPU開発ロードマップを進めている。これは、1年ごとに「アーキテクチャの刷新」「プロセスルールの移行」という2つの異なるCPU開発を交互に行うもので、CPUの進化をプロセルルールとアーキテクチャに分けて行うことで、無理のない技術革新を進められるというメリットがある。

現行の「Westmere」はプロセスルールを進める「Tick」世代にあたり、アーキテクチャ的には「Nehalem」世代をほぼ踏襲している。次世代の「Sandy Bridge」はアーキテクチャを刷新する「Tock」の世代にあたり、Nehalemを改良したアーキテクチャが採用されることになる。

これまでに明らかになっているSandy Bridgeの仕様について、最も注目されているのがCPUコアとGPUコアを1つのダイに統合したIntel初のメインストリームCPUという点だ。

Westmereでも1つのCPUにCPUコアとGPUコアが同居しているが、こちらは2つの異なるチップを組み合わせて1つにパッケージングしただけであり、機能的には独立して動いている。Sandy Bridgeでは、CPUとGPUが完全に統合され、さらにプロセスルールも統一される。WestmereではCPUコアが32ナノメートルプロセスルールであるのに対し、GPUとチップセットは45ナノメートルプロセスルールと異なっていた。これがSandy Bridgeでは32ナノメートルプロセスルールに統一する。

以上は、IDF 2010の開催前までに判明している情報だ。IDF 2010で公開された「Sandy Bridgeの詳細情報」で、特に注目を集めたのが「リングバス」だ。

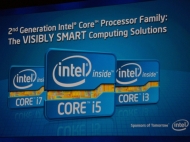

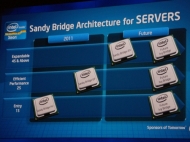

Sandy Bridge世代のCPUは、第2世代のCoreプロセッサファミリーとして、新しいロゴでプロモーションを展開する(写真=左)。サーバ向けSandy Bridgeのロードマップでは、ローエンドから順番にリリースされ、2ソケット対応の「Sandy Bridge-EP」が2011年後半、4ソケット以上の「Sandy Bridge-EX」が2012年以降になるとみられる。このあたりはNehalemのときと同じ移行スピードといえる(写真=右)

Sandy Bridge世代のCPUは、第2世代のCoreプロセッサファミリーとして、新しいロゴでプロモーションを展開する(写真=左)。サーバ向けSandy Bridgeのロードマップでは、ローエンドから順番にリリースされ、2ソケット対応の「Sandy Bridge-EP」が2011年後半、4ソケット以上の「Sandy Bridge-EX」が2012年以降になるとみられる。このあたりはNehalemのときと同じ移行スピードといえる(写真=右)GPUを強化する内蔵キャッシュと「リングバス」

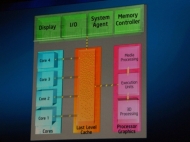

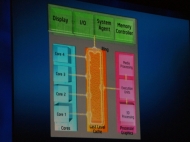

Sandy Bridgeの新情報として発表された「リングバス」では、CPU内部のキャッシュメモリにリング状の通信経路を設け、ここに、CPUコアやGPUコア、メモリコントローラなど各種コントローラが接続する。リング型バスは信頼性が高く、通信の「渋滞」が発生しにくいことでパフォーマンスを得やすい。これにキャッシュメモリを組み合わせることで、複数のコアが存在するCPU内部での通信をさらに高速化するのが狙いとみられる。

この構造で最も恩恵を受けるのがGPUコアで、従来のチップセット内蔵型GPU(iGPU)で問題だったDRAMへのメモリアクセスがリングバスにあるキャッシュメモリによって削減することで、アクセスの高速化が期待できる。ほかにも、CPUコアを含めて処理がリングバスのキャッシュメモリ内で完結している間は外部への通信が最小限度で抑えられるため、アプリケーション次第ではパフォーマンスの向上が期待できるという。

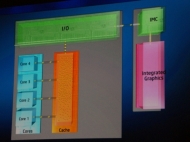

Sandy Bridgeのダイとパルムッター氏(写真=左)。従来までのCPUとGPUの構成図。互いに独立した関係にある。これは現行の「Westmere」でも同様で、CPUダイとチップセット、そしてGPUダイが1つにパッケージングされているだけだ(写真=中央)。このCPUとGPUを1つのダイで統合するとこうなる。これが「Sandy Bridge」だ(写真=右)

Sandy Bridgeのダイとパルムッター氏(写真=左)。従来までのCPUとGPUの構成図。互いに独立した関係にある。これは現行の「Westmere」でも同様で、CPUダイとチップセット、そしてGPUダイが1つにパッケージングされているだけだ(写真=中央)。このCPUとGPUを1つのダイで統合するとこうなる。これが「Sandy Bridge」だ(写真=右)

IDF 2010で展示されたSandy Bridgeのウェハ(写真=左)。IDF 2010でCPUコアとキャッシュ、GPUコアとを連結する「リングバス」の仕組みが初めて公開された。キャッシュを介してCPUコアとGPUコアが高速接続されたことで、アプリケーション次第ではGPUパフォーマンスの大幅な向上が期待できる(写真=右)

IDF 2010で展示されたSandy Bridgeのウェハ(写真=左)。IDF 2010でCPUコアとキャッシュ、GPUコアとを連結する「リングバス」の仕組みが初めて公開された。キャッシュを介してCPUコアとGPUコアが高速接続されたことで、アプリケーション次第ではGPUパフォーマンスの大幅な向上が期待できる(写真=右)関連キーワード

Sandy Bridge | CPU | GPU | Intel | Intel Developer Forum | Intel Turbo Boost | Westmere | Nehalem | 次世代 | デュアルコア | クアッドコア | 32nmプロセス | ポール・オッテリーニ | Intel HD Graphics

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- ワコムが有機ELペンタブレットをついに投入! 「Wacom Movink 13」は約420gの軽量モデルだ (2024年04月24日)

- わずか237gとスマホ並みに軽いモバイルディスプレイ! ユニークの10.5型「UQ-PM10FHDNT-GL」を試す (2024年04月25日)

- 「社長室と役員室はなくしました」 価値共創領域に挑戦する日本IBM 山口社長のこだわり (2024年04月24日)

- 「Surface Go」が“タフブック”みたいになる耐衝撃ケース サンワサプライから登場 (2024年04月24日)

- QualcommがPC向けSoC「Snapdragon X Plus」を発表 CPUコアを削減しつつも圧倒的なAI処理性能は維持 搭載PCは2024年中盤に登場予定 (2024年04月25日)

- 16.3型の折りたたみノートPC「Thinkpad X1 Fold」は“大画面タブレット”として大きな価値あり (2024年04月24日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- アドバンテック、第14世代Coreプロセッサを採用した産業向けシングルボードPC (2024年04月24日)

- AI PC時代の製品選び 展示会「第33回 Japan IT Week 春」で目にしたもの AI活用やDX化を推進したい企業は要注目! (2024年04月25日)

- ロジクール、“プロ仕様”をうたった60%レイアウト採用ワイヤレスゲーミングキーボード (2024年04月24日)