「第2世代FXは2012年。28ナノプロセスは2013年」──AMD、2013年までのロードマップを公開:頼りにするのは“Piledriver”と“Streamroller”(2/2 ページ)

省電力APUは“Piledriver”を採用してTDP 17ワットを目指す

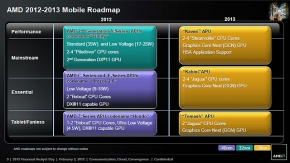

ノートPCとタブレットデバイス向けのCPUでは、パフォーマンス級とメインストリーム級の上位から中位シリーズでも、Fusion APUの第2世代Aシリーズ「Trinity」を投入し、TDP 35ワットモデルとTDP 17ワットモデルを用意する。“Piledrive”コアを2〜4基実装し、DirectX 11に対応する“第2世代”グラフィックスコアを統合する。

メインストリーム級の下位シリーズからエッセンシャル級では、Brazos 2.0世代のFusion APU EシリーズとCシリーズが登場する。TDPは9ワット、または、18ワットと従来のBrazosと同様で、デュアルコアの“Bobcat”CPUとDirectX 11対応のグラフィックスコアGPUを統合する。

タブレットデバイスとファンレスデバイス向けでは、開発コード名「Hondo」世代のFusion APU Zシリーズが2012年後半に登場する。TDPは4.5ワットになる予定で、シングルコア、またはデュアルコアの“Bobcat”CPUコアとDirectX 11対応グラフィックスコアを統合する。

2013年になると、Trinity、Brazos 2.0、そして、Hondoのそれぞれは、Kaveri、Kabini、そして、「Temash」に切り替わる予定だ。KaveriとKabiniはデスクトップPC向けにも登場するFusion APUで、Temashも28ナノメートルプロセスルールを導入し、デュアルコアの“Jaguar”CPUコアとGraphics Core Nextアークテクチャのグラフィックスコアを統合する。

Piledriverのサーバ導入は2012年後半から2013年に

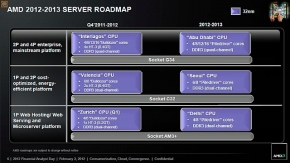

サーバ向けCPUでは、2Pと4P対応のSocekt G34プラットフォームで、“Interlagos”シリーズの後継として“Abu Dhabi”シリーズが2012年の後半に登場する。Piledriver世代のCPUコアを4基/8基/12基/16基実装するモデルを用意する予定で、メモリコントローラはDDR3対応クアッドチャネルをサポートする。1Pと2P対応のSocket C32プラットフォーム向けの“Valencia”シリーズも、“Seoul”シリーズに切り替わる。Piledriver世代のCPUコアを6基、または、8基実装するモデルが2012年後半に登場する予定で、メモリコントローラはDDR3のデュアルチャネル対応だ。

マイクロサーバ向けのSocket AM3+プラットフォームでは、4コア、または、8コアの“Bulldozer”を実装する“Zurich”シリーズが2012年の前半に登場する。ただ、このクラスは、2012〜2013年にPiledriverコアを採用する“Delhi”シリーズを2012年に投入する予定だ。コアの数は4基、または、8基で、メモリコントローラはDDR3のデュアルチャネル対応と、Zurichと共通する。

Komodo、Krishna、Wichitaのキャンセルを正式に確認

なお、今回のFinancial Analyst Dayでは、デスクトップPC向けのAM3+対応CPUで、“Piledriver”を6〜10コア実装する“Komodo”や、Bobcatの後継となる28ナノメートルプロセスルール採用Fusion APUの省電力クラスとして開発を進めていた“Krishna”とWichta“、そして、KrishnaとWichtaを採用するプラットフォームとして予定していた“Deccan”などの開発コード名が、「NO LONGER IN USE」として扱われていることも明らかになった。

関連キーワード

CPU | Bulldozer | GPU | Interlagos | Valencia | AMD | APU | ロードマップ | 28nmプロセス | AMD Fusion | Radeon | Bobcat | Brazos | Krishna | Radeon HD 7000シリーズ | タブレットPC | サーバ向けプロセッサ | Hondo | コンパクトPC

関連記事

大解説! 28ナノプロセスルール採用の新世代GPU「Radeon HD 7970」

大解説! 28ナノプロセスルール採用の新世代GPU「Radeon HD 7970」

AMDが“Southern Islands”と呼んで開発を進めてきた新世代GPUの最上位モデル“Tahiti”を発表した。その詳細をオースティンであった説明会から紹介する。 2011年は28ナノ世代に注力、そして20ナノ世代へ――GLOBALFOUNDRIESの事業戦略

2011年は28ナノ世代に注力、そして20ナノ世代へ――GLOBALFOUNDRIESの事業戦略

旧AMDの製造部門から分社したGLOBALFOUNDRIESは、台湾のTSMCやUMCに並ぶ、世界最大規模のファウンダリ企業。2011年以降、プロセスルールの微細化をどう進めるのか。 2011年のAMDは“APU”で総攻撃

2011年のAMDは“APU”で総攻撃

AMDが2010年のFinancial Analyst Dayを開催した。金融アナリスト向けだが、最新ロードマップと“決意”を示す重要な機会。今回はどんな決意を示しただろうか? Hot Chips 22で示されたAMDの次世代CPU“ブル&ボブ”

Hot Chips 22で示されたAMDの次世代CPU“ブル&ボブ”

米国で開催された「Hot Chips 22」で、AMDは「Bulldozer」「Bobcat」に関する講演を行った。そのスライド資料に次世代CPUコアの“新事実”はあるのか? Analyst Dayで分かった「Bulldozer」の強味

Analyst Dayで分かった「Bulldozer」の強味

Nehalem、Westmereと世代更新が進むインテルに対し、AMDは「2011年」まで待ちの構え。その2011年に大きく変化する新世代CPUの概要が明らかになる。 次の波は2011年に来る──Analyst Dayに見るAMDの進化速度

次の波は2011年に来る──Analyst Dayに見るAMDの進化速度

45ナノプロセルルールを導入した“Shanghai”が発表された11月13日に、AMDは「Analyst Day」を行った。ここでは、そこでアップデートされたロードマップを紹介しよう。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- ノートPCに外付けキーボードを“載せて”使える「タイプスティックス/打ち箸」に新色 (2024年04月18日)

- もう全部、裏配線でいいんじゃない? 「ASUS BTF DESIGN」が示す自作PCの新しい形 (2024年04月19日)

- バッファロー製Wi-Fiルーターに脆弱性 対象機種は今すぐファームウェア更新を (2024年04月17日)

- さらなる高速化を実現! PCI Express 5.0接続SSDの新モデル「Crucial T705」を試して分かったこと (2024年04月18日)

- ついに8K対応した「Insta360 X4」の画質をX3と1インチ360度版で比較 今買うべき全天球カメラだと確信した (2024年04月16日)

- SwitchBotのミニプラグに不具合 「断続的にオン/オフを繰り返す、異音」などで該当製品の交換を呼びかけ (2024年04月17日)

- アイロボットが4万円切りの「水拭き対応ロボット掃除機」を投入 “一家に1台”を目指す (2024年04月17日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- 「JBL GO 4」でBluetoothスピーカーデビュー! 累計出荷台数5700万台を突破した人気製品の最新モデルを試す (2024年04月17日)

- 無線LANルーター「Aterm」シリーズの一部に複数の脆弱性 設定変更や買い替えをアナウンス (2024年04月11日)