タブレット市場に注力するIntelのモバイルプロセッサ戦略:「3年先を行く」製造技術(2/2 ページ)

半導体製造技術で大きくリードするIntel

Intelの強みは、競合他社よりも優れた半導体製造技術を有していることにある。しかし、新生Intelは、その半導体製造技術を、今後はより広範に提供していく考えだ。

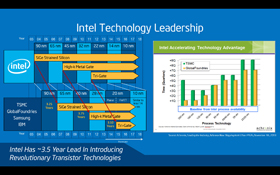

同社は、すでに14ナノメートルプロセスを立ち上げ、10ナノメートルプロセスの開発にも取りかかっているなど、プロセス技術では競合他社を大きく引き離している。また、2012年には、立体構造トランジスタ技術である3Dトライゲートトランジスタを実用化するなど、最先端の半導体製造技術を誇る。

Intelの半導体製造技術が、業界を大きくリードしていることは誰もが認めるところ。2015年には10nmプロセスを立ち上げる予定になっている。その同社の半導体製造技術を、他社にも供与する半導体製造サービスを本格的に展開する意向を示す

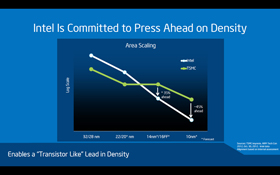

Intelの半導体製造技術が、業界を大きくリードしていることは誰もが認めるところ。2015年には10nmプロセスを立ち上げる予定になっている。その同社の半導体製造技術を、他社にも供与する半導体製造サービスを本格的に展開する意向を示す同社で半導体製造技術の開発や製造を統括するウィリアム・ホルト上級副社長は、同社が22ナノメートル世代で3Dトライゲートトランジスタ技術を採用したことにより、半導体製造技術が微細化するごとに、チップ面積を削っていく道筋を確立したが、競合他社は20ナノメートル以降、立体トランジスタ技術のFinFETを確立するまでは、配線パターンの微細化ができないため、チップサイズを小さくすることができず、チップの製造コストにも跳ね返ってくると指摘。Intelの製造技術が、競合他社よりも、3年強のアドバンテージを保っていると、その優位性をアピールする。

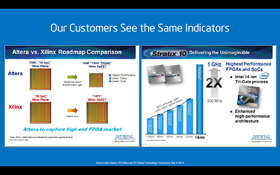

同社の半導体製造サービスについては、すでにAlteraが14ナノメートルプロセスを利用したFPGAを製造する計画を明らかにしているが、こうしたサービスを、より広範に提供していくことで、Intel最大の強みである半導体製造技術も、収益源としたい考えだ。

Intelの半導体製造サービスは、Intelアーキテクチャを採用するセミカスタムチップの開発だけでなく、フルカスタムのチップ開発にも利用できるように、その範囲を拡大(写真=左)。Intelは、3Dトライゲートトランジスタ技術の採用により、1xナノメートルプロセス台でもトランジスタの集積度を高め、トランジスタあたりのコストを低減できているが、競合他社は20ナノメートルプロセスから集積度やコスト面で苦戦するという分析(画面=右)

Intelの半導体製造サービスは、Intelアーキテクチャを採用するセミカスタムチップの開発だけでなく、フルカスタムのチップ開発にも利用できるように、その範囲を拡大(写真=左)。Intelは、3Dトライゲートトランジスタ技術の採用により、1xナノメートルプロセス台でもトランジスタの集積度を高め、トランジスタあたりのコストを低減できているが、競合他社は20ナノメートルプロセスから集積度やコスト面で苦戦するという分析(画面=右)

Intelの14ナノメートルプロセスを利用するAlteraは、チップの微細化を可能にするが、その競合となるXilinxは、16ナノメートルFinFETを利用してもチップサイズを縮小できず、コストがかさむという(画面=左)。Intelの製造プロセスは、競合他社よりも3年以上進んでおり、この技術を利用できるメリットは大きいとアピール(画面=右)

Intelの14ナノメートルプロセスを利用するAlteraは、チップの微細化を可能にするが、その競合となるXilinxは、16ナノメートルFinFETを利用してもチップサイズを縮小できず、コストがかさむという(画面=左)。Intelの製造プロセスは、競合他社よりも3年以上進んでおり、この技術を利用できるメリットは大きいとアピール(画面=右)しかし、半導体業界関係者は、Intelの半導体製造サービスを自社製品に利用できるベンダーはほとんどないだろう、と見る。その最大の理由として挙げるのが「これまでベールにおおわれてきたIntelの半導体製造技術に対応した半導体設計ツールがないことだ」と、大手半導体メーカー関係者は語る。

また、「Intelの半導体プロセスはCPU向けに特化しており、GPUやセンサーなど、広範に利用できる製造プロセスではない」(半導体製造ベンダー関係者)。それでも、今後Intelが、半導体製造サービスを前提に、プロセス開発を進めていくようになれば、高性能化のためには、より多くのトランジスタを必要とするGPUなどの高性能化を加速することが可能になる。しかし、「Intelの最先端プロセスを利用したい筆頭は、TSMCの半導体製造プロセスの進化が鈍化していることから、GPUの高性能化が難しくなっているNVIDIAだろう。しかし、HPC市場では最大のライバルとなる企業に対しても、同サービスを提供する“度量”があるのか、注目したい」と、業界関係者たちは、その動向を注視している。

関連記事

独走なるか:「Bay Trail-T」でライバルを突き放す――Intelのモバイルプロセッサ戦略

独走なるか:「Bay Trail-T」でライバルを突き放す――Intelのモバイルプロセッサ戦略

COMPUTEX TAIPEI 2013で、Intelは同社CPUの省電力性能をアピールするデモを実施。2013年後半に投入を予定しているタブレット向けSoC「Bay Trail-T」(開発コード名)を搭載した端末のリファレンスモデルも披露した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- バッファロー開発陣に聞く「Wi-Fi 7」にいち早く対応したメリット 決め手は異なる周波数を束ねる「MLO」【前編】 (2024年04月22日)

- MSIから裏配線マザーが2モデル登場! (2024年04月22日)

- OpenAIが日本法人を設立 日本語に最適化したGPT-4カスタムで3倍速く/Microsoft Edgeの更新で「Microsoft Copilot」アプリが導入される不具合 (2024年04月21日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- PFUのコンパクトキーボード「HHKB Professional HYBRID」が全品2000円オフのセール! (2024年04月20日)

- もう全部、裏配線でいいんじゃない? 「ASUS BTF DESIGN」が示す自作PCの新しい形 (2024年04月19日)

- ASUS×NoctuaのGeFroce RTX 4080 SUPER搭載カードがデビュー! (2024年04月20日)

- トランセンド、M.2 2242に対応したM.2 NVMe Gen4 SSD (2024年04月22日)

- ASUS、Wi-Fi 7に対応したハイエンド仕様のゲーミング無線LANルーター (2024年04月22日)

- 「IBMはテクノロジーカンパニーだ」 日本IBMが5つの「価値共創領域」にこだわるワケ (2024年04月23日)