| News | 2003年4月17日 05:58 PM 更新 |

本格的なスループットコンピューティングは2005年のNiagaraからスタート

サンが開発する「スループットコンピューティング」対応CPUは、インテルの超高度集約型CPUとはまったく逆のアプローチ。Yen氏は「インテルを攻撃してサンを持ち上げる」サンがお得意とするスピーチで熱弁をふるった

サン・マイクロシステムズ(以下 サン)は4月17日に東京の赤坂プリンスホテルにおいて、「Sun IT 基盤改革フォーラム」を開催した。このイベントは、現代のITインフラに求められる「TCOの削減」「投資リスクの最小化」「システムのシンプル化」を実現する、サンのITソリューションを紹介するもの。

このイベントに合わせて来日したExecutive Vice President Processor and Network ProductのDavid W.Yen氏が記者会見を行い、サンのCPU戦略について説明した。講演の内容は、基本的に今年の2月に米国で行われたアナリスト向け年次カンファレンスで述べらたものだが、スループットコンピューティングに関するまとまった発表は、基盤改革フォーラムが初めてになる。

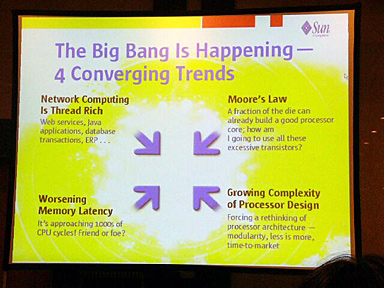

サンが主張するCPU開発における四つのトレンド。スレッドの増大、レイテンシの増大、無駄なトランジスタの増大、CPU構造の複雑さの増大、これらの問題を解決するのがシンプルなCPUをモジュールで組み合わせるスループットコンピューティングだ

Yen氏は、コンピュータ開発において、現在大きな四つのトレンドがあると紹介。第1のトレンドは、ネットワークの普及でシステム内部に発生する「大量のスレッド」だ。「サーチエンジンやネットオークション、ネットショッピングなどを利用するユーザーが激増することで、膨大なスレッドがサーバマシンに要求されている。しかし、今のほとんどのCPUはシンプルなので、限定的な作業をこなしているに過ぎない。そのため、複数のCPUを相互に接続して、たくさんのスタックを構成して膨大なスレッドを処理している」とYen氏は現状を分析する。

第2のトレンドは、「CPUの構成トランジスタ数は2年で2倍になる」というムーアの法則の束縛だ。Yen氏は「このペースでいくと2007年には10億個のトランジスタでCPUを構成しなければらない。しかし、処理速度を上げるには、その10分の1のトランジスタで十分」と、パフォーマンスの視点では、ムーアの法則は破綻しつつあると主張。「余ってしまうトランジスタをどのように使うべきか、インテル自身が真剣に悩んでいる」と競争相手を攻撃したうえで、「これからは、まったく新しい考え方が必要になる。それが、マルチスレッドとマルチプロセッシングなのだ」と、スループットコンピューティングの必然性をアピールした。

第3のトレンドは、CPUの高速化に伴なう「メモリレイテンシの悪化」。CPUの動作クロックは3GHzに達してしまったが、メモリは依然としてギガクラスを超えられない。これからもCPUとメモリのギャップは開いていき、メモリレイテンシの値は増大すると考えられる。Yen氏は「プリフェッチといった、従来の方法によるメモリのデータ転送高速化の手法も、この問題を解決できない」と、レイテンシを削減するのではなく、別な方法でパフォーマンスを改善する必要性を説いた。

第4のトレンドは、極度に複雑化するCPUアーキテクチャの弊害だ。あまりにも構成が複雑化したために、求めれる開発リソースは人間の能力をはるかに超えてしまっている、とYen氏は語る。「インテルのItaniumのように高度にトランジスタを集約しなくとも、設計の方向性を変えてモジュラー的構造にすれば、もっとシンプルで高いパフォーマンスを発揮するCPUを開発できる」とシンプルなプロセッサコアをモジュール的に組み合わせる方向性を示した。

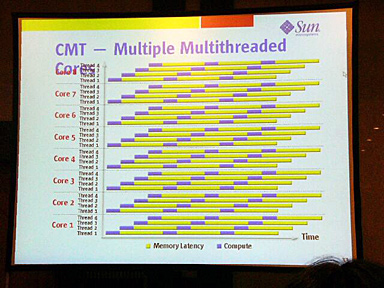

以上の問題点を解決する方法として、サンは以前から「スループットコンピューティング」を提案していた。これは、一つのダイにシンプルなコアを複数実装し、さらにそれぞれのコアで複数のスレッドを発生させるもの。各スレッドを少しずつずらして進行させるため、一つのスレッドのレイテンシタイムに別なスレッドの処理をCPUに行わせることができる。コア全体としてメモリレイテンシが隠蔽できる仕組みだ。

このようにスレッドをずらして発生させ、CPU処理のタイミングを調整する。この仕組みは、Hyper-Threading テクノロジ対応Pentium 4ですでに実現されている。2005年に登場するNiagaraでは、一つのダイに8ユニットのCPUコアが実装される予定。画面ではそれぞれのコアで四つのスレッドを発生させているが、これはサンが考える1コアユニットあたりの最適スレッド数に基づいている

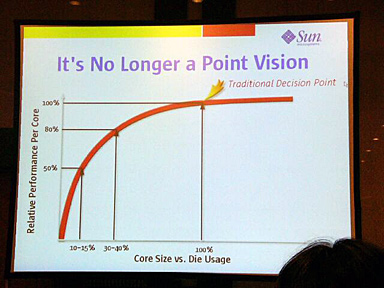

CPUのパフォーマンスはトランジスタが多ければ多いほど高くなる。しかし、直線的に比例するわけでなく「ダイサイズ100のときのパフォーマンスを100とすると、コアサイズ10〜15でパフォーマンスは50程度発揮できる。しかし、コアサイズを30〜40にしてもパフォーマンスは80程度で、コアサイズとパフォーマンスの効率は悪くなる」と、Yen氏は、大きなコアと一つのコアのパフォーマンスより、小さなコアを複数搭載した場合のパフォーマンスが高いという、スループットコンピューティングのメリットを説明している。

コアサイズとパフォーマンスの関係を示したグラフ。横軸はダイサイズに対するコアサイズの割合。縦軸はコアサイズ=ダイサイズのパフォーマンスを100とした場合のパフォーマンスの割合。コアサイズが大きくなるにつれて、パフォーマンスの伸びは鈍ってくるのが分かる

スループットコンピューティングを成功させる必須要素として、Yen氏は「コンシューマーでなく、マルチスレッドが求められるサーバシステムにフォーカスすること。十分なメモリ帯域を確保すること。Solarisのような優れたマルチスレッド対応OSが使えること。顧客に対してロードマップ情報を適宜提供できること」と述べ、サンがこれらの条件を可能にする、すべてのリソースを持っていることをアピールした。

サンが現在公開している、CPUロードマップで「CMT design」としているのは、2003年から2004年に登場が予定されている「UltraSPARK IV」から。また、2004年に登場するブレードサーバ向けの新ラインナップ「Gemini」もCMT Designとされている。ただし、Yen氏によると「これらはスループットコンピューティングCPU第1世代と言えるが、従来のUltraSPARC IIIコアを二つ実装したに過ぎない。本当のスループットコンピューティングCPUは、まったく新しいデザインでなければならない。その意味では2005年に登場する「Niagara」が最初の本格対応CPUとなるだろう」としている。

「構成がシンプルになることで、パイプラインのステージも少なくなるのか」という質問について、Yen氏はそれを認めた上で「ステージが多くなると、レイテンシも多くなる」と、長いパイプラインのデメリットを強調した。また、90ナノプロセスの登場が2005年と、インテルよりも遅いことに関して「インテルは予定であって、実際に製品が出てくるかは分からない。サンのロードマップはCPU単体でなく、システム全体の出荷時期を説明している」と、とくに問題と考えていないと答えた。

記者会見を行ったDavid W.Yen。エンタープライズサーバの分野で活躍した後に、SPARCの開発、戦略、マーケティングの統括業務に携わっている

関連記事

関連リンク

[長浜和也, ITmedia]

Copyright © ITmedia, Inc. All Rights Reserved.