| News | 2003年9月30日 08:52 PM 更新 |

Charteredがナノプロセスルールのロードマップを発表

半導体ファンダリーのChartered SemiconductorがIBMと協同による65ナノプロセス半導体開発を先日発表したが、そのロードマップやファウンドリーサービス「NanoAccess」の内容の詳細を明らかにした。

Chartered Semiconductor(Chartered)は、9月18日に発表した90ナノプロセス対応ファウンドリー製造プロセスサービス「NanoAccess」とNanoAccessをサポートする企業連合「NanoAccessアライアンス」に関する国内説明会を9月30日に行った。

すでにCharteredはIBMと協同で90ナノプロセスの半導体開発を行うことを明らかにしているが、NanoAccessでは半導体開発のデザインルールマニュアルやスパイスモデルをIBMとまったく共通にすることで、IBMとCharteredの両方から同じレベルの90ナノプロセス技術をクライアントに提供できるようになっている。

説明会に登場した同社のケビン・メイヤー氏(Worldwide Marketing & Services Vice President)はNanoAccessアライアンスの説明に先立って、「多くの半導体メーカーが90ナノプロセスの開発に参入することで、これからは製品の差別化がもっとも重要な問題になるだろう」と半導体開発の動向について説明した。

「半導体プロセスが微細化するにしたがって、集積されるトランジスタの数は数千万というオーダーになってきている。膨大なトランジスタを組み合わせる複雑な半導体になると、製造コストよりも設計コストで生産者は悩むようになるだろう」(メイヤー氏)

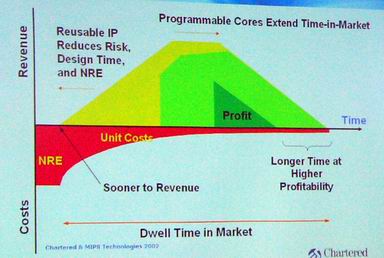

このように現在の半導体開発では、増える一方の設計コストとマスクコストをいかにして抑えるかが課題となっている一方で、クライアントからは、短い製品寿命でも利益を確保できるように、初期コストの低減と製品の延命を可能にするプログラマブルコアの採用、そして納入された製品が短期間で立ち上げられる「一発動作」の要求も日に日に強くなっている。

半導体開発に占める設計、マスク、製造コスト割合の推移。0.35マイクロプロセスで1割程度だった設計とマスクのコストが、90ナノプロセスでは6割を占めるまでになっている

ある半導体製品の製品寿命における売り上げとコストの関係。製品が短命になってきている現状では、どれだけ出荷前の初期コスト(NRE)と立ち上げの時間を抑えられるが利益に大きく影響する

この「短期間で利益をあげるために、短期間で製品を立ち上げる」のは、最近の複雑を極める生産現場では困難を極める作業。NanoAccessでは、90ナノプロセスルールで半導体を設計したいクライアントに対して、IBMと協力して作成した「デザインルールマニュアル」や、設計シミュレーションで使うスパイスモデルを提供し、開発時間を短縮する。

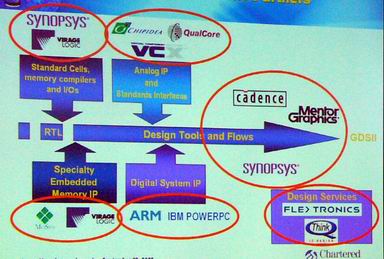

さらに、「すでにこのような技術を確立させて“知的資産”を所有している複数の企業で、それぞれ得意とする工程や分野の技術情報などを共有するための企業連合を組織した」と、メイヤー氏はNanoAccessアライアンスのアドバンテージを説明している。

開発の各工程で分業で協力するNanoAccessアライアンスパートナー。日本からも大日本印刷、凸版印刷グループなどが参画している

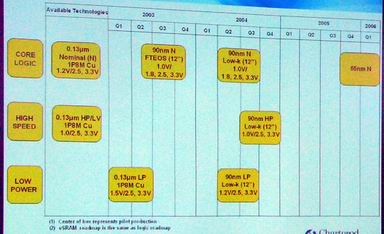

続いて登場したジョン・マーティン氏(Strategic Alliances & Partners Vice President)は、Chateredのロジックテクノロジーのロードマップを説明した。

Charteredが進めているロジックテクノロジーには、通常(Nominal)、高性能、低消費電力といった三つのタイプが用意されている。Charteredのロードマップによると、通常タイプで層間絶縁膜にFTEOSを採用した90ナノプロセスは今年の10月から受注を開始、層間絶縁膜に低誘電体を採用した通常、および低消費電力タイプの90ナノプロセスを2004年の第2四半期に提供を開始する予定になっている。高性能タイプの90ナノプロセス(低誘電体採用)は少し遅れて第3四半期になる見込みだ。

また、90ナノプロセスのスパイスモデルも高性能タイプを除いてすでに用意ができている(高性能タイプのスパイスモデルは2003年第4四半期の予定)。

Charteredが説明会で示したロードマップ。65ナノメートルプロセスのサービス開始は2005年の第4四半期。ただし、本格的な普及の時期としては「90ナノは2005年から2006年にかけて。65ナノはその後になる」とCharteredは予測している

現在、IBMとCharteredの混成チームによって90ナノメートルプロセスの生産技術の構築作業が進められている。米ニューヨーク州にあるIBMの工場B323ラインでは、IBMが持っていた200ミリウェハラインを300ミリウェハラインへスケールアップする作業がすでに終了しており、2003年の年末から2004年にかけてCharteredの「Fab7」にB323のラインを忠実にコピーした300ミリウェハラインを構築する予定になっている。

「共通のデザインルールに従い、プロセスや製造装置を正確にコピーしたIBMとCharteredのラインで生産される半導体は、まったく同質の製品になる」(マーティン氏)ことで、IBMとCharteredはスケールメリットによるさらなるコストダウンも目指している。

IBMとCharteredの生産技術移設フロー。スライドには「トランスファ」と書かれているが、実際の内容は説明にもあるように「忠実なコピー」となる。現在は90ナノプロセスの半導体を生産するが、将来予定されている65ナノ、45ナノプロセス半導体生産にも対応できる予定だ

関連リンク

[長浜和也, ITmedia]

Copyright © ITmedia, Inc. All Rights Reserved.