| News | 2003年11月6日 02:29 AM 更新 |

「これで10年は寿命が延びた」ムーアの法則

インテルの最新技術は、すべて「ムーアの法則」を実現するために開発されている……。セミナーで登壇した技術者たちは、自分たちの説明を「これで10年間は大丈夫」という言葉でまとめている。

11月5日に東京で行われた「インテル・テクノロジ・セミナー」では、インテルが新しく開発した「High-k」「メタルゲート」を利用するトランジスタの特性解説を始めとして、まもなく登場する90ナノメートルプロセス半導体で利用されている技術や、次々世代を目指したマスク技術など、主に生産技術に関する最新の状況が紹介された。

インテルの城浩二氏(取締役開発製造技術本部長)は、最近の生産技術に関する研究成果によって「ムーアの法則は10年先まで通用する目処がついた」と述べるほどに、インテルにとって「ムーアの法則」は依然として重要な道しるべとして認識されている。「2010年には操作周波数20GHz、トランジスタ数は10億個以上」(城氏)が求められる半導体のプロセスは、これからも2年ごとにダウンサイズを進めていくことになる。

城氏の説明によると、インテルが描いているプロセスサイズのロードマップでは2003年に65ナノプロセス、2007年の45ナノプロセスの導入がそれぞれ予定されている。

また、90ナノプロセスで50ナノであるゲート長は、現在、研究所レベルで15ナノのプロトタイプ試作を成功させており、「あとは大量生産に関する課題を解決するのみ」という段階まで達している。2007年に登場する予定の45ナノプロセスのゲート長が25ナノ以下と予想されているので、さらにその先の微細化まで実現の目処が立っていることになる。

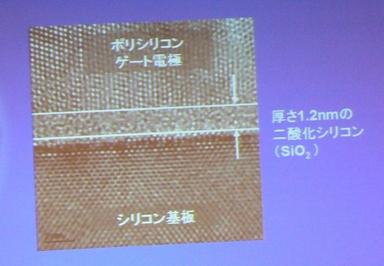

セミナーで紹介された90ナノプロセスを実現する技術その1「厚さ1.2ナノメートルのゲート酸化膜」。二酸化シリコン膜の厚さは原子5個分。この薄さゆえ「漏れ電流」の発生が大きな問題になっている。これを解決するために開発されたのが、「High-k」「メタルゲート」なのだ

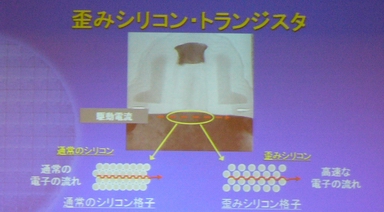

90ナノプロセスを実現する技術その2「歪みシリコントランジスタ」。通常整然と並んでいるシリコン格子に「ある物質を混入することで」(城氏)1〜2%の隙間を生じさせ、高速な電子の流れを可能にする。トランジスタの駆動電流を10〜20%向上させて、プロセスの微細化に大きく影響している技術だが、「混入する物質や製造方法は秘密」(城氏)

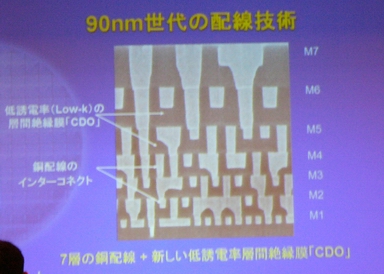

90ナノプロセスを実現する技術その3「7層の銅配線とCDO」。0.13マイクロプロセスまで6層だった銅配線を7層にして、層間絶縁膜には低誘電率の「CDO」(Carbon Doped Oxide)を新しく採用した。CDOの採用によって配線容量が従来の20%削減され、より高速な信号伝達が可能になっている。また、これまで4層構造だった層間膜の構造を2層にすることで、コストの低減も実現した

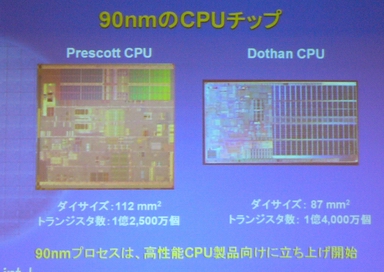

90ナノプロセスを採用する予定のPrescottとDothan。サンプル出荷は開始されているらしいが、製品の発表は年末から来年になるものと見られている

High-Kとメタルゲートを使った半導体開発の説明は、このセミナーのために来日したIntelのロバート・S・チャウ氏(フェロー兼技術・製造本部トランジスタリサーチディレクタ)によって行われた。

High-k(高誘電率材料)をゲートの絶縁膜に使うのは、プロセスの微細化によって大きな問題となりつつある「漏れ電流」を抑制するため。現在は「理想的な素材で、代替え素材への移行は心臓移植にも匹敵する」(チャウ氏)と開発者に言わしめる二酸化シリコンが使われている。

しかし、微細化に伴う薄膜化が原因で発生する漏れ電流を抑えこむために、インテルは「厚くて」「大量の電流を流せる高誘電率」な素材をゲートの絶縁膜に採用した。インテルのデータではHigh-kを採用した場合、誘電容量は従来より60%アップしゲートの漏れ電流は100分の1までになった。

効率が向上し漏れ電流が減るのだから、すぐにでも採用したいHigh-k絶縁膜だが、これまでゲート電極の素材として使われているポリシリコンと組み合わせると、トランジスタを動作させるしきい電圧が上昇する現象が発生する。これでは駆動電圧が高くなってしまうわけで、省電力とパフォーマンスに大きく影響してしまう。

また、High-k素材の物性的問題でポリシリコンと接触させるとHigh-k絶縁膜の内部で「フェノン振動」が発生し、電子の流れを阻害する問題も発生する。

これらの問題を解決するために採用されたのが「メタルゲート」。しきい値の向上とフェノン振動を解決し、かつ駆動電流を大量に流せる半導体が実現できるようになった。現在量産に向けた開発が進められており、2007年に登場する45ナノプロセストランジスタで採用される予定になっている。

左が従来の二酸化シリコンを使った構造で右がHigh-kを使った場合の構造。High-kの絶縁膜の厚さは3ナノに達する

インテルが80ナノプロセストランジスタで測定したドレイン電流とゲート電圧の関係

このほかセミナーでは、開発製造技術本部のリソグラフィ開発部長である大藤武氏から「先の先」の半導体の生産に必要になるEUV(極紫外線)用マスク技術についての説明や、テクノロジーソリューションセンター部長の石川公也氏による、パッケージングテクノロジーの説明が行われた。

インテルのマスク技術ロードマップでは、透過光を利用して193ナノメートルの露光波長を利用しているが、現在、パターン寸法のほうが小さい状況が続いている。2007年からはEUV露光を実用化し、一気に露光波長を13ナノまで引き下げる予定になっている

EUV露光を利用したマスク。従来の光フォトマスクではは透過光を利用していたが、EUV露光では反射光を利用する

関連記事

[長浜和也, ITmedia]

Copyright © ITmedia, Inc. All Rights Reserved.