RISC-Vの誕生 既存の命令セットアーキテクチャでは満足できなかった、その理由:RISCの生い立ちからRISC-Vまでの遠い道のり(2/3 ページ)

いよいよ、連載タイトルにも入っている「RISC-V」の登場である。

プロセッサはRISCベースであることはこれまでと一緒だが、特徴として、

- IEEE754-1985準拠の浮動小数点演算、及びCommon Lispのサポート

- SPURのコアそのものは汎用プロセッサ

とされる。

SPURのS、つまりSymbolic ProcessingはおそらくCommon Lispのサポートから来ていると思うのだが、Lisp専用機(多分Symbolics 3600のことを指しているのだと思う)は逆に汎用性が低いという欠点は当時から言われており、なので汎用コアにLisp処理と浮動小数点演算(この2つが同等に並んでいる、というあたりが今では考えにくい)のアクセラレータを付け加えたような構成を志向したものになっている。

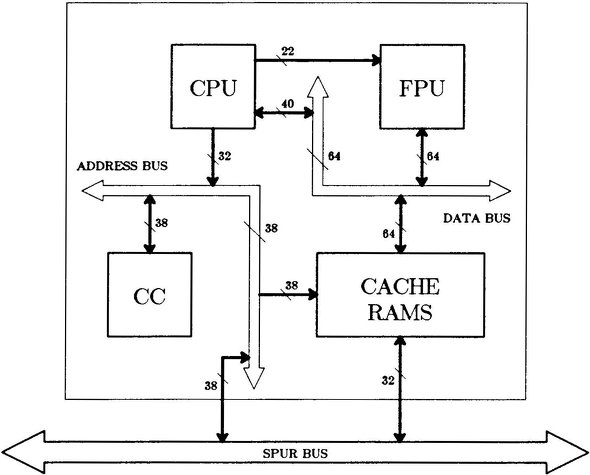

ちなみにパイプラインはRISC-I/IIの3ステージから1段増えて4ステージになっており、より高速動作を狙っている。ただ当時のプロセス(2μm CMOS:最終的には1.6μm CMOSで製造)ではさすがにFPUはおろかキャッシュコントローラー(CC)の内蔵も難しく、それもあってCPUボードは3つの専用チップ(CPU+FPU+CC)に、200ほどのStandard ICを組み合わせた構成になったそうだ(写真6)。

アドレスバスは38bitという不思議なものだが、個々のCPUが32bitアドレスで、うち30bitが仮想アドレス(正確には12bitがオフセット、18bitが仮想ページナンバー)、2bitがSegmentへのIndexとなっている。このSegmentは8bit構成になっており、なので個別のCPUは30bitの仮想アドレス空間を持ち、システム全体では38ビットの仮想アドレス空間となる設計である。プロセッサそのものも、理論上は最大253プロセッサまで利用可能となっていた。

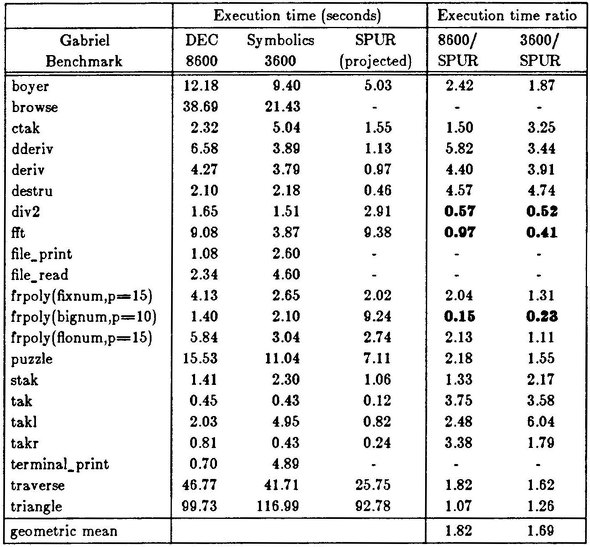

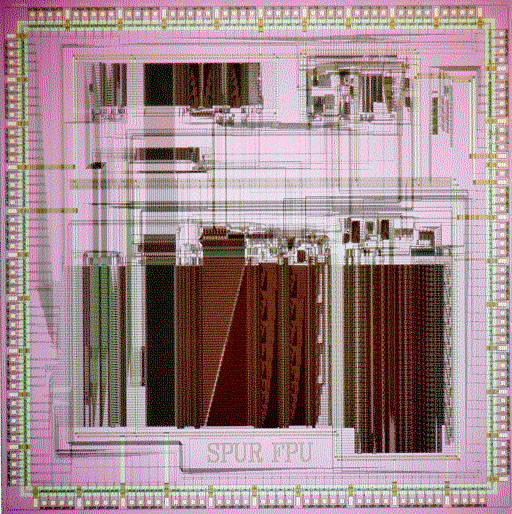

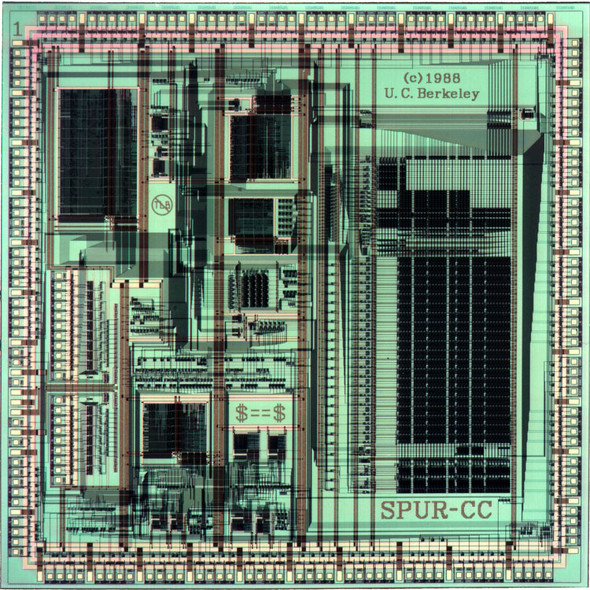

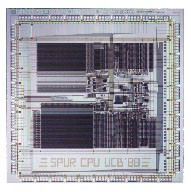

SPURは10MHzでの動作を予定していたが、その性能はVAX 8600やSymbolics 3600と比べても十分高速、というのがシミュレーションでの結果(写真7)である。最初の論文は1985年に出ているが、この時点で基本的な論理設計はほぼ完成していたようだ。その後は物理設計に入り、1988年にはチップも完成している(写真8〜10)。ちなみにSPURはこのチップを作って完成というわけではなく、その後もいろいろ研究は続いたが、おおむね1990年ごろにはほぼ終了していたと思われる。

写真8:CPUチップ。レイアウトはRISC-IIによく似ている気がする。ダイサイズは170平方mm、11万5214トランジスタで構成される。出典は“Berkeley Hardware Prototypes”(PDFへのリンク)

前出のSOARをRISC-III、SPURをRISC-IVとして数えたときに、5番目となるRISC-Vがアサノビッチ教授のRaven-1となる。Raven-1はSPURから実に23年ぶりとなる、久々のプロセッサ開発である。別にパターソン教授がその間サボっていたというわけではなく、その後もRAID-I、VLSI-BAM、RAIDE-II、Torrent-0、Tertiary Disk、NOW-2などさまざまな研究プロジェクトを行っているが、商用RISCチップが世の中に出回るようになると、これを使って何かをする、という方向性に変わっていったようだ。

加えていえば、一度商用ベースで開発が始まるとすぐに競争が激化し、すごいスピードで開発が進むようになるから、同じことを大学でやってもキャッチアップしきれなくなる。なので、それこそRaven-1のように相当先端的なことをやるのでない限り、大学でCPUそのものを作るというメリットが薄れてきた、となるのは否めないだろう。

CPUの設計そのものは、冒頭でも書いたようにFPGAをターゲットとして実施できるし、昨今ではFPGAのロジックゲート数がハイエンド品では1千万に達している。これだけあれば、少なくとも学生が数カ月で設計するCPUであればまず使い切ることはできない(膨大なキャッシュとかを実装すれば使い切ることは可能だろうが)。

なので、LSIの設計を行う教育は普通に行われているが、それをLSIとして製造する必要がなくなった、というのが正確なところかもしれない。逆にアサノビッチ教授のプロジェクトは、FPGAを使っている限り、まず実現できないもので、だからこそ28nmのFD-SOIで製造を行う必要性があったわけだ。

Copyright © ITmedia, Inc. All Rights Reserved.