| News | 2003年6月12日 07:05 PM 更新 |

インテルが30ナノメートルプロセスのトライ・ゲート・トランジスタの開発に成功

プロセルルールの細微化が進む現状でも「ムーアの法則」を生き残らせるために、インテルはナノテクノロジを駆使してプロセッサの開発に挑んでいる。今回発表されたトライ・ゲート・トランジスタによって、また一歩新世代プロセッサの実現に近づいた。

インテルは6月12日、新しいトランジスタ技術である「トライ・ゲート・トランジスタ」の詳細を発表した。なお、今回の発表は、来日している米インテル 技術開発本部上席フェローのマーク・ボア氏によって、京都で開催されている「2003 Symposia of VLSI Technology and Circuits」と、東京のMarunouchi Cafe地下に設けられた会場で同時に行われた(東京会場は電話会議システムを使用)。

トライ・ゲート・トランジスタについては、すでにインテルによって2002年に発表されているが、今回の発表では従来60ナノメートルだったゲート長が30ナノメートルまで縮小された。試作されたトライ・ゲート・トランジスタで計測された値は、シミュレーションで予想されたものとほぼ一致しており、インテルはこの結果から「研究段階は終了し、開発段階に入った」とコメントしている。

インテルでは、早ければ2007年にも実用化を目指している45ナノメートルプロセスにおいて、このゲート技術を採用する可能性があるとしている。

現在のトランジスタはプレーナー型といい、ゲートを一つしか有していない。プロセスの微細化が進むにつれ、ゲートも小さくなり、そこを流れて供給される電流も少なくなる一方だ。

ところが、それに伴ない電流がゲートを通過するときに発生するリークの問題が大きくなってきている。インテルは「現在のシングルゲートのプレーナー型トランジスタでは、プロセスが30ナノメートルになった段階で、リークによる損失のために、所定のパフォーマンスが出せなくなる」と考えている。

このため、複数のゲートを実装させて供給電流量をふやす「マルチ・ゲート・トランジスタ」の研究が各半導体メーカーで進められている。インテルが進めている「トライ・ゲート・トランジスタ」以外にも、IBMとAMDがゲートを二つ実装した「ダブル・ゲート・トランジスタ」を開発している。

どちらも供給電流を増やし、リークを減少させるメリットは同じだが、プレーナー型ではゲート長の3分の1とされていたシリコンの薄さが、ダブル・ゲート型では3分の2、トライ・ゲート方では3分の3と、トライ・ゲート型はより厚いシリコンでも形成可能となっている。

仮に30ナノメートルプロセスで考えた場合、プレーナー型では最厚でも17ナノメートル、ダブル・ゲート型で20ナノメートル、トライ・ゲート型で 30ナノメートルという値になる。インテルによれば「このことが、トライ・ゲート型ならほかの方式より、製造が簡単で大量生産に向いていることを示している」(ボア氏)。

従来からある平面構造のプレーナー型トランジスタ(画面上)では、上面に配置された一つのゲートでしか電流を供給できなかったが、ダブル・ゲート・トランジスタ(画面左下)やトライ・ゲート・トランジスタ(画面右下)では、複数のゲートで電流を流せ、リークも少なくできる

シリコン内部を流れる電流量をシミュレートした結果。上面にしか電流が流れないプレーナー型に対して、左右側面にも電流が流れるトライ・ゲート型のメリットがよくわかる

インテルは、今回の2003 Symposia of VLSIで、CMOSによる無線技術に関する内容と、低消費電力と高性能を両立させる新しい回路設計に関する内容に関する発表も併せて行った。

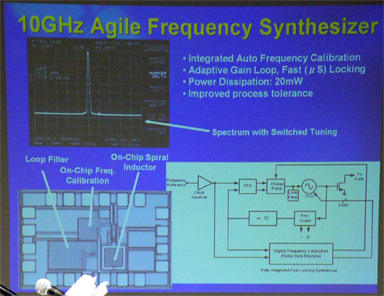

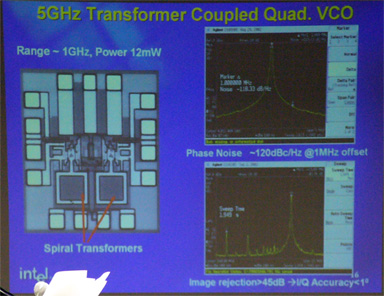

CMOSによる無線技術については、すでに6月9日行った無線技術の研究に関する記者説明会とほぼ同じ内容。今回はとくに10GHz対応の周波数シンセサイザーと5GHz動作の発振器について、試作機で測定された波形を使い、品質のデータを交えながら説明を行った。

10GHz対応周波数シンセサイザー。左上の波形は、試作機でチューニングされたスペクトラム。きれいに1波だけが立ち上がっている理想的な形になっている

インテルが開発した「5GHz Transformer coupled VCO(電圧制御発信機)のM6層(画面左)に、ノイズ(画面右上)と精度(画面右下)の測定グラフ。従来のVCOと異なり、トランジスタではなくトランスフォーマ(変圧器)を利用することで性能が向上。VCOの精度はQuadratureとIn-Phaseの位相差が90度の場合に理想とされているが、従来90度±2度程度だったものが試作機では90度±1度未満を実現している。

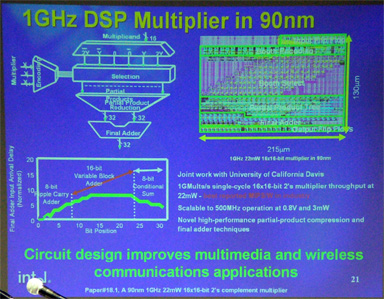

新しい回路設計に関する発表では、現在の開発課題が低電力で高い性能を発揮し、かつ漏れ電流を少なくすることにあると述べた上で、世界最高のMIPS/ワットを実現した1GHz DSP Multiplier回路や、漏れ電流を46%削減した6.5GHz Dual Supply Register Fileを紹介した。

22mVの動作電圧で1GHzを発揮するDSP Multiplier

画面右上にあるグラフが、今回試作された6.5GHz Dual Supply Register Fileにおける、供給電圧と漏れ電流の関係を示したもの。1.2V供給と0.9V供給を比較すると電圧低下は25%でしかないのに、漏れ電流は46%の削減されている

関連記事

関連リンク

[長浜和也, ITmedia]

Copyright © ITmedia, Inc. All Rights Reserved.