| News | 2003年7月11日 11:31 PM 更新 |

Rambusはメモリの仇をPCI Expressで討つ

次期製品の展示やセミナープログラムも用意されていたが、残念ながらRDRAMがメモリの主役になることはないだろう。その代わりにRambusはPCI Expressに期待をかける。なんたってフォーラム2日めの主役に抜擢したのだから。

7月10日から開催されている、Rambus Developer Forum Japan 2003。初日のプログラムでは、XDR DRAMにフォーカスを当てたMain SessionとTechnical Trackが設けられ、XDR DRAMの詳細仕様やロードマップが公開され注目を集めた。

2日めは、PC向け次期インタフェースである「PCI Express」と高速データ通信がメインテーマとして取り上げられた。PCI Expressについては、Technical Trackの講演者として登場したRambusのAnil Godbole氏(Logic Interface Division Technical Marketing Manager)が「もし、PCI Expressそのものについて詳しく知りたければ、インテルのイベントで聞いてください」と発言するぐらい、これまで開催された技術系セミナーイベントで繰り返し紹介されている。

きょうのTechnical Trackでは、もう一歩踏み込んだ実際の開発で必要になる、PCI Express PHYの仕様や、PCI Expressのパラレルインタフェース用PIPEの実装方法の解説が行われた。その意味では真の「Developer Forum」的内容といえるだろう。

PCI Expressは、サーバ用高速パラレルバスのPCI-Xや、PCの外部機器接続バスとして最も普及しているPCIと、ソフトウェアレベルで互換性を持たせることになっている。そのため、シリアル接続のPCI Expressにパラレルインタフェースへの変換回路も実装する必要があるのだ。

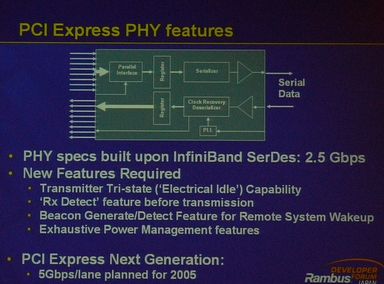

PCI ExpressのPHY層ブロック図。パラレルで入力してきたデータをシリアルに変換して送信、受信したシリアルデータはクロック情報とデータに分割し、データをパラレルに変換する。PCI ExpressはInfiniBandをベースに、PCで必要になるプラグ&プレイ機能やパワーマネジメント機能を拡張している

PCIのパラレル接続では、データとクロック情報はそれぞれ専用線を使って送受信されるが、PCI Expressでは、データとクロック情報は一緒のケーブルを使って送受信される。そのため、PCI ExpressのPHY層にはシリアルとパラレルの変換やデータとクロック情報の統合、分離復元を行う、Phisical Coding Sublayer(PCS)が設けられている。

PCI Expressを構成するレイヤー。PHY層はさらにLogic層とElectrical層に分かれる

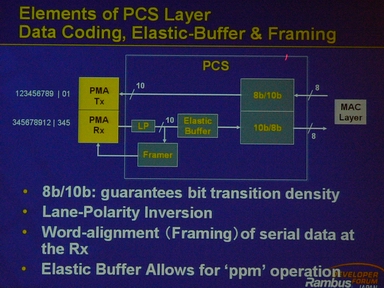

Electrical層はデータの送受信を行うPHA(Physical Media Attachment Layer)と、データの変換などを行うPCSに分かれる。PCSの上位にMAC層が位置する

PCSの内部構成。Elastic BufferからFramerを経てPMA Rxに信号が送られているが、これは動作クロックのズレ補正情報をFramerに渡し、データフレームの切り出し情報としてフィードバックするためだ

PCSを構成する主なユニットは、パラレルとシリアルの変換で使われる8b/10bエンコードデコードユニットと、受信したデータ配列からデータ位置を切り出すFramerユニット、そして、データを送受信するシステム間におけるクロックの違いを補正するElastic Bufferユニットの三つ。

ちなみに、PCI Expressでサポートするパラレル接続のデータ転送レートは、データ幅10ビット時で250MHz、もしくはデータ幅20ビット時で125MHzと規定されている。データ幅が8ビット、もしくは16ビットでないのはPCS内部で8b/10bエンコードされて10ビット幅でMAC層に送られるためだ。

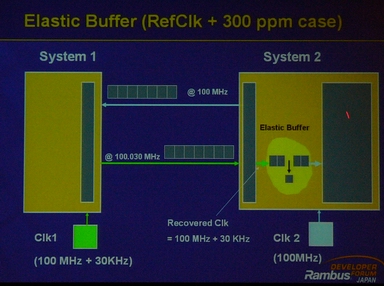

PCSを構成するユニットの中で、最も重要になるのがElastic Bufferユニット。PCI Expressで接続されるシステム(これはマザーボードとそこに増設されているPCI Express対応拡張カードでもいい)では、送受信パケットの中に組み込まれたクロック情報をやり取りするが、この情報を利用して、接続されたシステム間でクロックのズレが発生している場合に、Elastic Bufferの内部で送受信するフレームにビットを追加、もしくは削除してデータの一貫性を保つようにする。

この仕組みによってPCI Expressでは、仮に正規のクロックが100MHzだった場合、±30KHzまで補正できるものとしている。

相手側(画面ではSystem1)のクロックが速い場合、Elastic Bufferでは余計に送られてくるビットを間引きしてデータの同期を図ろうとする。逆に相手側のクロックが遅い場合は、Elastic Bufferで足りないビットを追加する

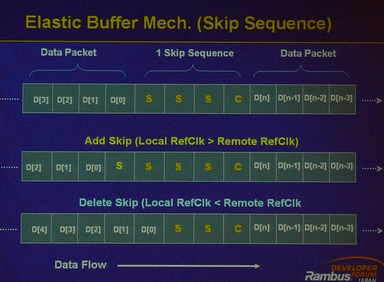

Elastic Bufferのビット増減は、データフレームに設けられたSkip Sequence用のビットに対して行われる。一番上は正規のビット配列で真ん中が1ビット追加された状態、下が1ビット間引きされた状態のデータ配列になる

ここで紹介したPHY層が出来てしまえば、PCI Expressへの移行は技術的にそれほど大変なことではない。データリンク層まで接続してしまえば、ドライバは従来のPCIバスと同じように認識してくれる。

PCI Express推進陣営は、既存のPCIと互換を取ることによって、開発者の労力を軽減させ、短期間でPCI Expressへの移行を進めようとしている。たしかに、これは開発者にとって非常に魅力的な仕組みになっている。さらに、開発が行いやすいということは、当然開発コストが削減され販売価格にも影響してくるはずだ。

もちろんエンドユーザーにとって、いまあるPCIベースのリソースがそのまま使えるメリットの大きさついては、改めて言うまでもないだろう。

関連記事

関連リンク

[長浜和也, ITmedia]

Copyright © ITmedia, Inc. All Rights Reserved.