| News:ニュース速報 | 2002年3月8日 04:19 PM 更新 |

シャープ,パッケージを多段積層する3次元SIPを開発

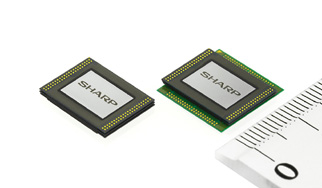

シャープは3月8日,LSIを収納したパッケージを多段積層できる3次元システムインパッケージ(SIP)技術を開発したと発表した。チップの積層化を発展させたもので,モバイル端末の小型化などに貢献できる。

まずスタックドCSP(Chip Size Package)で培った技術を基に,1パッケージに2チップを積層化したものとしては業界最薄の0.5ミリのパッケージを開発。このパッケージを多段積層する技術も開発し,5チップ以上の積層化を可能にした。例えば携帯電話で使われる複合メモリ2個(スタックドCSP)とベースバンドLSI1個の組み合わせをSIP1個で置き換えることができ,実装面積を半分に減らせる。パッケージの厚さは,積層5チップで最大1.4ミリ,6チップでも最大1.5ミリ。同社はメモリを収納したパッケージや,ASIC搭載パッケージについて端子配置の業界標準化を提案する。

関連記事

![]() シャープ,4チップ積層CSPを量産化

シャープ,4チップ積層CSPを量産化

関連リンク

[ITmedia]

Copyright © ITmedia, Inc. All Rights Reserved.