ニュース

Apple Silicon M2を外側から眺めてみて分かった、その性能の源泉とM3の可能性(1/3 ページ)

Armをはじめとするプロセッサの動向に詳しく、RISCプロセッサ、Apple Silicon連載記事も執筆した大原雄介さんに、Appleが発表したApple Silicon M2プロセッサの中身を、今ある情報から推測してもらった。

担当松尾氏より、いつものごとく「おつかれさまです。WWDC22でM1/M2のハイエンドが出たら、その解説記事をお願いできますか?」という依頼が飛んできたので、簡単にM2の詳細を眺めてみたい(分析、というほどには深くない)。

WWDC22で公開された情報全体のまとめはこちらになるが、この中でM2についてのみここではもう少し眺めてみたい。

Appleが今回M2に関して公開した情報はこちらにまとまっているが、

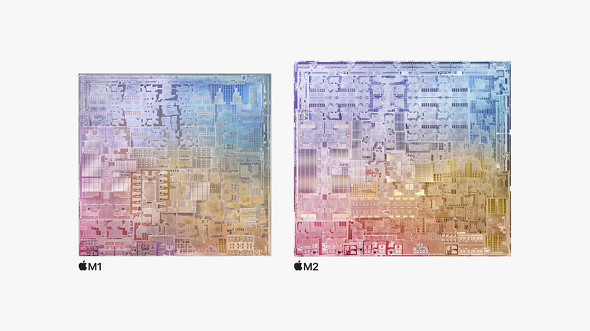

- 製造プロセスは引き続きTSMC N5、トランジスタ数は200億個で、これはM1より25%多い(写真1)。

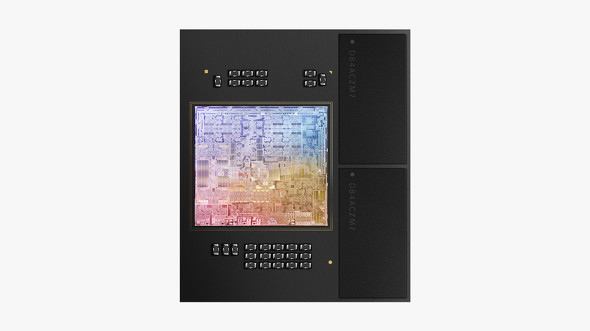

- Unified MemoryはM1比で50%増しの帯域100GB/secで、容量は最大24GB(写真2)。

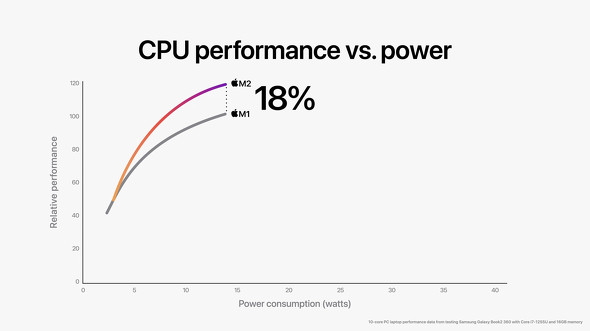

- Performance コアはキャッシュを大型化。またEfficient Coreの性能を向上。これにより、Multi-Thread Performanceが18%向上(写真3)。

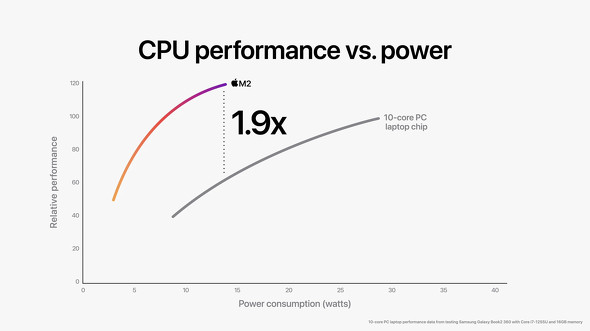

また10コアの競合製品と比較して、同じ15W枠だと1.9倍の性能(写真4)。

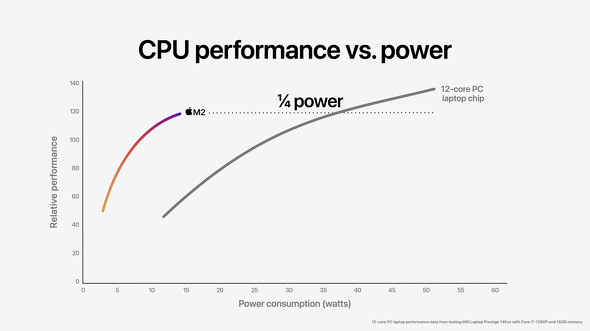

12コアの競合製品と比較して、同じ性能なら1/4の消費電力(写真5)だとする。

Copyright © ITmedia, Inc. All Rights Reserved.