Silverthorneは「1ワット2GHz駆動」を目指す:元麻布春男のWatchTower

まもなく始まるISSCC(国際固体回路会議)でIntelは多数の論文を発表する。そのなかには、“Silverthorne”に言及するものも用意される。

具体的な姿が見えてきた「Silverthorne」

2月4日から開催されるISSCC(国際固体回路会議)で、Intelは15件の論文を発表する。これらは、プロセッサ・テクノロジー、ワイヤレス・テクノロジー、メモリ・テクノロジー、テラスケール・テクノロジー、プロセス・テクノロジーの5つの分野にまたがる(プロセス・テクノロジーの論文は、IEDMで発表された論文の再録)。

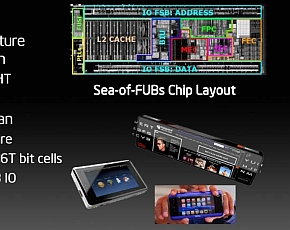

この中で最も注目を集めそうなのは、2007年春のIDFで発表された組み込み向けの省電力CPUである「Silverthorne」(開発コード名)の概要発表だろう。Silverthorneは、45ナノメートルプロセスルールで製造されるMID(Mobile Internet Device )、もしくは、UMPC(Ultra Mobile PC)向けのCPUだ。チップセットの「Poulsbo」と合わせ、「Menlow」プラットフォーム(いずれも開発コード名)を構成する。すでにダイ画像が公表されているほか、MenlowベースのMIDのモックアップや実動デモ機も披露されている。

しかし、その詳細となると、「自社現行プラットフォーム比で性能を10%向上させつつ発熱は4分の1に抑える」といった相対的な数値が示されるばかりで、具体的なスペックは明らかにされていなかった。今回も学会発表ということで、マイクロアーキテクチャや性能指標に関する詳細は明らかにされていないが、いくつかの興味深い事実が明らかにされている。

まず注目されるのは、Silverthorneのマイクロアーキテクチャがハイパースレッドをサポートする2命令同時発行イン・オーダー・パイプラインであることだ。IntelのCPUは、Pentium Pro(P6マイクロアーキテクチャ)以降、アウト・オブ・オーダー実行をサポートしてきた。つまり、プログラムに記述された順番通りに順次実行する(イン・オーダー)のではなく、記述順にかかわらず実行可能な命令から実行していく(アウト・オブ・オーダー)ことで、処理サイクルあたりの命令実行数(IPC)を高めてきた。

アウト・オブ・オーダー実行は、IPCを高めるのに効果的であり、特にシングルスレッドアプリケーションの性能向上に貢献する。半面、アーキテクチャが複雑化してトランジスタ数が増えるため、電力効率の点では必ずしもベストではない。x86系CPUでも、組込み用途向けのVIA C7などは、あえてアウト・オブ・オーダー実行をサポートせず、イン・オーダー実行のみとなっているのは、低消費電力を意識しているからだろう。1〜2ワット程度の消費電力を目指すSilverthorneも、電力効率を重視した結果、イン・オーダー・パイプラインを選択したものと思われる。

Intelのイン・オーダー・パイプラインのCPUとなると、Pentium(P5マイクロアーキテクチャ)以来となる。Pentiumも最大で2命令同時処理が可能であったが、すべてのx86命令で同時に処理できたわけではなかった。Silverthorneの2命令同時処理にどのような制限があるのか(あるいはないのか)は、現時点では明らかにされていない。

ただし、1つの物理CPUを2個の論理CPUに見せるハイパースレッドのサポートが加わっていること、命令セットが「Core 2 Duo完全互換」とされていることから考えて、まったく新規にデザインされたことは間違いなさそうだ。x64モードのサポートやSSE命令のサポートも当然あると思われる。SSE命令のバージョンがどこまでサポートされるのかについては現時点で明らかでないが、Penrynで導入されたC6ステートがSilverthorneでもサポートされていることを思えば、SSEも最新の4.1まで対応している可能性が考えられる。

Silverthorneでは、このC6ステートのサポートに加えてレジスタファイルの最適化と6T SRAMキャッシュの採用、GTL+に加えCMOSモードをサポートしたFSB、I/O電源の分離などの技術を用いることで、超低電圧版Pentium M(Dothan)の10分の1の省電力を実現するとされている。Silverthorneの動作クロックなどは、まだ明らかにされていないが、将来1ワットの消費電力で2GHz動作が可能になるといわれている。

高速化がさらに進むメモリ技術

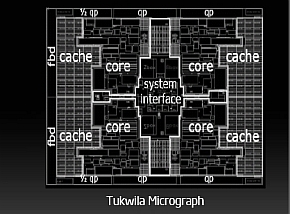

Silverthorne以外では、65ナノプロセスを用いたItanium 2(Tukwila:開発コード名)の概要、メモリではMLCをサポートした相変化型メモリ(PCM)、DDRインタフェースの導入によるNANDフラッシュメモリの高速化、2T構成とすることで2GHz動作と128Gバイト/秒の帯域を実現した組み込み用DRAM技術(Gain-Cellメモリ)などが目につく。20億トランジスタを集積したTukwilaは、計30Mバイトのキャッシュメモリを搭載、Nehalemで採用される予定のQuickPathインターコネクトを採用する。

PCMは、電圧をかけることで結晶状とアモルファス状を遷移する物質を用いたメモリで、2007年の年末からサンプル出荷が始まっている。開発パートナーであるST Microelectronicsとの共同である今回の発表では、結晶とアモルファスの中間状態を検知するアルゴリズムを開発、4つの形質をサポートすることで1つのセルあたり2ビットのMLCを実現した。

一方、高速NANDフラッシュメモリ用のDDRインタフェースは、IntelとMicron Technology(両者は合弁でNANDフラッシュメモリ製造会社であるIM Flash Technologiesを設立したパートナー)が共同開発したもので、ONFI 2.0規格に採用される見込みだ。2Tの高速DRAMは、SRAMによるオンダイキャッシュと、DRAMによる外部メインメモリの中間的な性能だが、現在のDRAMと異なりロジックの製造プロセスとの統合が容易で、マイクロプロセッサの設計に新たな可能性を切り開くものと期待されている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Centrino生誕の地、イスラエルのFabに行く(後編)

Centrino生誕の地、イスラエルのFabに行く(後編)

イスラエルのインテル拠点を巡礼する元麻布氏。前回訪れた「Haifa Validation Center」を後にして、今回は45ナノプロセスの製造拠点に向かう。 Centrino生誕の地、イスラエルのFabに行く(前編)

Centrino生誕の地、イスラエルのFabに行く(前編)

Intelのイスラエル拠点、と聞くと、なにかしら“謎のベール”に閉ざされているようなイメージが(勝手な妄想)。元麻布氏はイスラエルのFabでなにを見たのか。 限りない“膨張”を強いられるフラッシュメモリメーカー

限りない“膨張”を強いられるフラッシュメモリメーカー

Intelは巨大だ。1人で何でもできるし1人で何でもやっつけてしまえる。しかし、その巨人でもフラッシュメモリ事業では1人で生き残ることはできないのだ。 見えてきたPenrynとNehalemの「革新性」

見えてきたPenrynとNehalemの「革新性」

インテルが45ナノCPUとして予定している「Nehalem」は「Pentium Pro」以来の変革が施される。そのキーワード“組み合わせ”はCPUに何をもたらすのだろうか。 IntelはWiMAXを促進するのか阻害するのか

IntelはWiMAXを促進するのか阻害するのか

ノートPCの利用形態を大きく変化させるWiMAXは近い将来ノートPCのプラットフォームに統合される。しかし、そのことがWiMAXの可能性をつぶしかねないのだ。 45ナノで知るIntelとAMDの“工場哲学”

45ナノで知るIntelとAMDの“工場哲学”

45ナノプロセスルールを採用したCPUは、インテルから2007年に、AMDから2008年に登場するといわれている。その“タイムラグ”に両社の開発思想を見る。 Intelが45ナノ「Penryn」ダイ画像を公開

Intelが45ナノ「Penryn」ダイ画像を公開

Intelは2007年に投入予定の45ナノプロセスルールプロセッサの試作と動作確認を発表。「Penryn」スペックの一部も明らかにした。 インテルのアイルランドFabを“非”公式に訪れてみた

インテルのアイルランドFabを“非”公式に訪れてみた

元麻布春男氏が最新PC事情を分析する本連載。今回はスペシャル版と題して、アイルランドにあるインテルのFab 24に“ひっそり”と訪問した。- 「元麻布春男のWatchTower」バックナンバー: