| エンタープライズ:ニュース | 2003/02/10 20:27:00 更新 |

インテル初のデュアルコアプロセッサ「Montecito」はMcKinleyとソケットコンパチに

米インテルはサンフランシスコで開催される国際固体素子回路会議において、次世代Itanium 2「Madison」および「Montecito」に関していくつかの発表を行う。

米インテルはサンフランシスコで2月10日から開催されるISSCC(International Solid-State Circuits Conference:国際固体素子回路会議)において、夏にリリース予定の次世代Itanium 2「Madison」および2005年リリース予定の「Montecito」に関していくつかの発表を行う。

ISSCCは電気・電子関係ででは世界でもっとも大きな学会であるIEEE(Institute of Electrical and Electronics Engineers)の下部組織SSCS(Solid-State Circuits Society)が主催する国際会議で、毎年この時期に開催されている。

インテルは今回、名誉会長のゴードン・ムーア氏が10日に基調講演を行うほか、12の論文を発表する予定。この発表の中で、次世代のItanium 2に関していくつかの事実を明らかにするという。

第3世代Itanium「Madison」

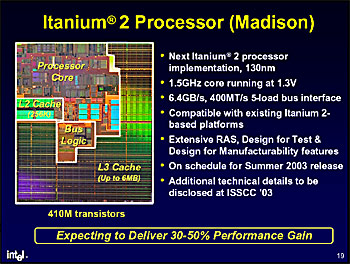

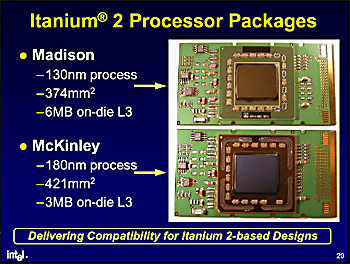

インテルは1月に、2005年までのItaniumプロセッサファミリ(IPF)ロードマップを発表している。Madisonは、現行のItanium 2「McKinley」の後継となる、2003年夏にリリース予定のプロセッサ。McKinleyが、180ナノメートルプロセスで製造され、1.5Mバイトまたは3Mバイトのオンダイ3次キャッシュを搭載するしているのに対し、Madisonは130ナノメートルプロセス、最大6Mバイトのオンダイ3次キャッシュを備えている。

動作クロックは5割増の1.5GHz、トランジスター数はほぼ倍増の4億1000万となっている。ただし、チップの面積ではMcKinleyの421平方ミリメートルに対して、374平方ミリメートルと小さくなっている。消費電力はコア電圧が1.5Vから1.3Vに下がったこともあり、130Wで変わらない。パフォーマンスではMcKinley比で30〜50%向上するという。Madisonは、3次キャッシュは3Mバイト、4Mバイト、6Mバイトの3種類のモデルを用意する予定。なお、数カ月前からOEM向けにサンプル出荷を開始しているという。

2004年にリリース予定のMadison 9Mは、Madisonと同じ製造プロセスを使い、オンダイ3次キャッシュを9Mバイトまで拡張したもの。動作クロックも1.5GHz以上になるとしている。

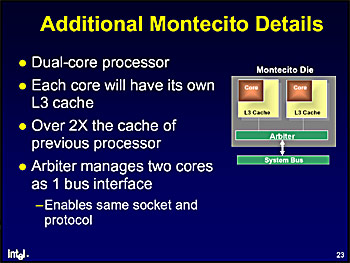

「Montecito」の概要はIDF Springで

Montecitoは2005年にリリース予定。90ナノメートルプロセスで製造し、インテルとして初めて、1つのシリコン上に2つのプロセッサコアを搭載するデュアルコアプロセッサになる。インテルが明らかにしたところによると、Montecito上の2つのプロセッサコアはそれぞれ独立した3次キャッシュを持っており、少なくともMadison 9Mの倍の18Mバイト(9Mバイト×2)またはそれ以上になるという。

また、Montecitoのソケット(ピン配置)やバスインタフェースプロトコルはMcKinley、Madisonとの互換性を持っており、基本的にはMcKinleyからのアップグレードが可能という。ダイ上の2つのプロセッサコアとシステムバスの間にはArbiter(調停器)と呼ぶ回路があり、プロセッサコアのシステムバスへのアクセスを制御する。

Montecitoに関しては、2月末に開かれるIntel Developer Forum Spring 2003でさらに情報を開示する予定としている。

「Deerfield」はMadison後に登場

なお、今後のIPF開発の方向性だが、高速化、より大きなキャッシュ、ローパワー化、デュアルコア技術、マルチスレッディングなどを挙げている。従来ロードマップで提示していた、ローパワーでローコストのItanium「Deerfield」については、Madisonリリース後に登場の予定。

関連記事関連リンク

[佐々木千之,ITmedia]