Intel,携帯/PDA向けのXScaleチップを発表(2/2)

| 【国内記事】 | 2002年2月12日更新 |

PDA向けの「PXA250」,携帯向けの「PXA210」

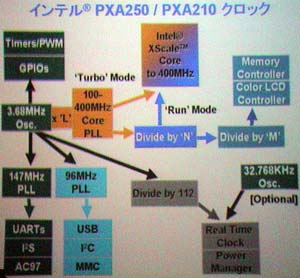

PXA250,PXA210は,細かな電力制御により低消費電力を実現している。コア電圧の変更はもちろん,動作周波数も変更できる。さらに「最高動作周波数と低い動作周波数を瞬時に切り替えることができる」(Intel)ターボ・モードを搭載した。

XScaleコアは,供給されるクロックに応じてさまざまな周波数で動作させることができる。PXA250/PXA210の場合,3.68MHzのオシュレータでクロックを発生させ,PLLで変化させてコアに提供している。同時に,PLLが生成したクロックは定数で割られて,メモリコントローラや液晶コントローラに提供されている。

PLLが生成した最高速のクロックと,メモリコントローラ用などに割り算されたクロックの両方をXScaleコアに提供できるようにし,この2つを瞬時に切り替えられるようにしたのがターボモードだ。

単純に,コアに提供するクロックを定数で割ることで,周波数を下げることも可能だが,「(割り算の)定数を変えるには,数10マイクロ秒かかる」(Intel)。定数の変更を行わず,最初から2種類のクロックを用意することで切り替えを高速にした。

「ターボモードとランモードは,それぞれPLLがロックしている。そのため切り替えが高速」(Intel)

例えば3.68MHzクロックを108倍し,400MHzを作り出す。ターボモードではこのクロックをそのままコアに提供する。また同時にクロックを4で割り,100MHzを作り出す。この100MHzがランモードとしてコアに提供される。

PXA250/210のクロック生成の流れ

PXA250のブロック・ダイアグラム。内蔵されるカラー液晶コントローラは,SVGAサイズ,16ビットカラーに対応している。IrDAやBluetooth用のインタフェースを持っており,これらはUART(汎用シリアルポート)としても利用できる。汎用ピンは15本。

PXA210とPXA250の違いは,16ビット/32ビット両用だった外部データバスが,16ビットのみになっていること。また汎用ピンも2本に減っている。これらの工夫によってピン数を減らし,パッケージサイズの小型化を図っている

両製品が備える主なインタフェース

| インタフェース | PXA250 | PXA210 |

| MMC/SDカード | ○ | |

| USB | ○ | |

| Bluetooth | ○ | |

| 携帯電話などのベースバンドチップ | ○ | |

| PCMCIA(PXA250のみ) | ○ | − |

XScaleコアの中身はどうなっているのか?

XScaleの特徴は,高クロック化に対応したアーキテクチャを持っているところにもある。低消費電力をウリとしながらも,1GHzという高クロックでも動作するという(2000年8月の記事参照),柔軟性の高さがXScaleコアの特徴だ。

XScaleのアーキテクチャは,英ARMのARMバージョン5.0に準拠しており,StrongARMなどのアーキテクチャ──ARMバージョン4と上位互換性を持っている(2001年8月の記事参照)。

Intelが独自にARMを拡張した部分もある。40ビットのアキュムレータ(累算器)を備えたマルチメディア演算ユニットがそれだ。ARMアーキテクチャでは,バージョン6でマルチメディア演算命令が追加されたが,「ARMバージョン6のマルチメディア命令との互換性はない」(Intel)。

マイクロアーキテクチャの部分でも,XScaleはStrongARMから大きな進化を遂げている。StrongARMでは5段だったパイプラインを,通常時で7段,データアクセス時で8段,マルチメディア演算時で10段と格段に増やし,動作クロックを向上させた。

PentiumのマイクロアーキテクチャP5では,パイプラインは5段。PentiumIIIのP6では10段。組み込み向けのプロセッサとはいえ,PC向けCPUと同様にクロックを向上させる複雑な仕組みが盛り込まれていることが分かる。

確かにパイプライン段数を増やせば,動作クロックは増す。しかしそれと同時に条件分岐の際にパイプラインがストールした場合のペナルティが増してしまう(2000年11月のPentium 4の記事参照)。

この“ブランチのペナルティ”に備え,「Xscaleでは,StrongARMにはなかった分岐予測バッファを搭載した」(Intel)。分岐の飛び先を予測して,先に命令をフェッチしてくることで,ペナルティを減少させる仕組みだ。

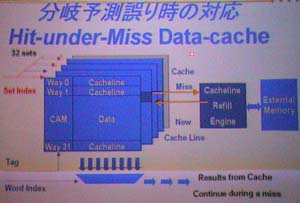

少しでもパイプラインを止めずに動かし続けるために,Hit-under-Miss Data-casheという仕組みも備えている

関連記事

![]() Intel,XScale積極推進――近く試作機を配布

Intel,XScale積極推進――近く試作機を配布

![]() 解説:さまざまなARMプロセッサ 〜16ビットから32ビットまで〜

解説:さまざまなARMプロセッサ 〜16ビットから32ビットまで〜

![]() Intel,超低消費電力のXScaleで日本のケータイ市場に進出

Intel,超低消費電力のXScaleで日本のケータイ市場に進出

![]() Intel,低消費電力・高性能の「XScale」チップアーキテクチャ発表

Intel,低消費電力・高性能の「XScale」チップアーキテクチャ発表

![]() インテル,XScaleアーキテクチャを使ったプロセッサを展示

インテル,XScaleアーキテクチャを使ったプロセッサを展示

![]() ARM,モバイル機器向け次世代アーキテクチャをIntelとTIにライセンス

ARM,モバイル機器向け次世代アーキテクチャをIntelとTIにライセンス

![]() Palm OSのARMアーキテクチャへの移行に向けて,Palmと大手チップメーカー4社が提携

Palm OSのARMアーキテクチャへの移行に向けて,Palmと大手チップメーカー4社が提携

関連リンク

![]() インテル

インテル

[斎藤健二,ITmedia]

Copyright © ITmedia, Inc. All Rights Reserved.

モバイルショップ

最新スペック搭載ゲームパソコン

最新スペック搭載ゲームパソコン

高性能でゲームが快適なのは

ドスパラゲームパソコンガレリア!

最新CPU搭載パソコンはドスパラで!!

最新CPU搭載パソコンはドスパラで!!

第3世代インテルCoreプロセッサー搭載PC ドスパラはスピード出荷でお届けします!!