| News | 2003年4月21日 11:38 PM 更新 |

「積極的な半導体設備投資は“PS2のおかげ”」――ソニー、2000億円投資で次世代チップ「CELL」製造へ

ソニーとSCEIが総額約2000億円の設備投資を発表。次世代プロセッサ「CELL」の生産を目指した今回の巨額設備投資は、ソニーグループが掲げるブロードバンド戦略にとって重要な位置付けとなる

ソニーとソニー・コンピュータエンタテインメント(SCEI)は4月21日、新プロセッサ「CELL」を中心としたブロードバンド対応システムLSI生産を行うための総額2000億円に及ぶ設備投資を発表した(別記事を参照)。またSCEIは同日、プレイステーション2用CPUとグラフィックチップを、90ナノメートルプロセスのDRAM混載プロセスで1チップ化していくことを明らかにしている(別記事を参照)。

今回の大規模設備投資の経緯や今後の半導体事業戦略などについて、ソニーの安藤国威社長とSCEIの久夛良木健社長が都内で記者会見を実施。半導体製造で協業を行う東芝セミコンダクターの藤井美英副社長も出席した。

都内で記者会見を実施したソニーの安藤国威社長(左)、SCEIの久夛良木健社長(中央)、東芝セミコンダクターの藤井美英副社長(右)

SCEIは2001年春から米IBM、東芝と共同で次世代汎用プロセッサ「CELL」の開発に取り組んでいる。CELLは、プレイステーション3など次世代コンピュータエンタテインメントシステムに搭載予定となっているソニーグループの中核技術。CELLの生産を目指した今回の巨額の設備投資は、ソニーグループが掲げるブロードバンド戦略にとって重要な位置付けとなるわけだ。

ソニーとSCEIが行う総額2000億円の設備投資は、世界最先端となる65ナノメートルプロセスと300ミリ(12インチ)大口径ウエハーを採用した半導体製造ライン導入に向けたもの。2005年度までの今後3年間で、3段階に分けて設備投資が実施される。新ラインではCELLプロセッサの開発後期における試作からスタート、段階的に量産体制を構築する。

「2003年度は第1段階として730億円をかけて、長崎にある半導体生産拠点“SCE Fab2”の1階約1万平方メートルのスペースに300ミリウエハーのラインを設置する。現在、SCE Fab2では0.18/0.15マイクロメートルの半導体製造を行っているが、今回の設備投資によって将来主流になると思われる65ナノプロセスを300ミリという大口径で実現する。第1段階の投資ではパイロットラインの設置のみで、65ナノプロセスへの本格的な展開は2005年以降になる予定」(久夛良木社長)。

長崎にある半導体生産拠点“SCE Fab2”で65ナノプロセスがスタート

世界最先端の65ナノメートルという超微細な製造プロセスを可能する要素技術が「EDRAM(Embedded DRAM)」と「SOI(Silicon On Insulator)」だ。

「それぞれに求められる要件や特性が異なることから、従来はDRAMとロジックとを別々に生産していた。だが、高速な処理が求められるブロードバンド向けプロセッサや、ハンドヘルド機器向けの低消費電力プロセッサを作るためには、DRAMとロジックを混載するEDRAM技術は、今後ますます重要になってくる」(久夛良木社長)。

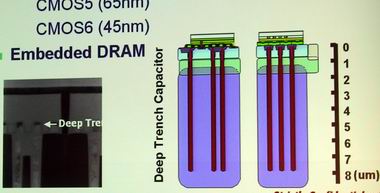

ソニーと東芝は、DRAMとロジックを混載したEDRAMの開発を共同で進めており、0.18/0.15マイクロメートルのEDRAM生産拠点を長崎のSCE Fab2に設置。現在、PS2向けのGraphics Synthesizer(GS)を量産している。さらに両社は共同で「Deep Tranch Capacitor」と呼ばれるEDRAMの微細化製造技術の開発を進めている。

「従来はキャパシタをシリコンの基板上に積み重ねていたのが、新技術ではシリコンウエハーの中に針を刺したような穴を作ってそこに誘電体を埋め込む“トレンチ構造”でDRAM混載プロセスの微細化を図っている。この技術で、90ナノ以下の製造プロセスにめどがたった。この新技術によって45ナノプロセスによるEDRAMまでも視野に入れている」(久夛良木社長)。

シリコンウエハーの中に誘電体を埋め込む“トレンチ構造”でDRAM混載プロセスの微細化を実施

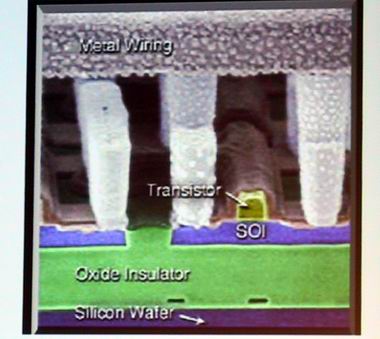

また、IBM、SCEI、東芝の3社は昨年4月に、各種機能を単一チップに集積した次世代半導体製造プロセス「SOI」の共同開発を表明している。

「SOIは、シリコン基板上に絶縁膜を形成してその上にトランジスタを作ることで、非常に低消費電力で高性能な半導体を作れる技術でネットワークプロセッサや信号処理プロセッサに最適。現在、90/65/45ナノに向けての開発を進めている。また、LSIの高速化と低消費電力化を実現する多層銅配線技術の開発も行っている」(久夛良木社長)。

各種機能を単一チップに集積した次世代半導体製造プロセス「SOI」

90ナノプロセスでEEとGSの統合チップ

65ナノプロセスに先行して導入される90ナノプロセスを生かしたのが、PS2コアの1チップ化だ。新チップはPS2の心臓部である128ビットRISC「Emotion Engine(EE)」と、DRAM内蔵並列グラフィックチップ「Graphics Synthesizer(GS)」、4MバイトDRAMを1チップに統合。ダイサイズが86平方ミリメートルと大幅に小型化しており、コスト低減と低消費電力化が図れるのが特徴だ。

新チップは、SCEIと東芝の合弁メーカー「大分ティーエスセミコンダクタ(OTSS)」で今春から製造を開始し、今秋にはSCE Fabでも生産を始める計画。 SCE FabとOTSSでは1999年以降、180ナノプロセスからプロセスルールを順次シュリンク、現在は90ナノプロセス対応ラインの敷設を進めている。

「90ナノプロセスによって、統合チップのほかにDRAMを混載したサウンドチップ(SPU2)や汎用RDRAMなどはOTSSとSCE Fabのどちらでも生産可能となり、従来は外部調達だったDVDデコーダやコントロールプロセッサもSCE Fabで作れるようになる。大きな設備投資のあとにシュリンクするとキャパシティの余剰が懸念されるが、シュリンクしていったものをこのような周辺チップに応用していくことでインテグレーションを図る」(久夛良木社長)。

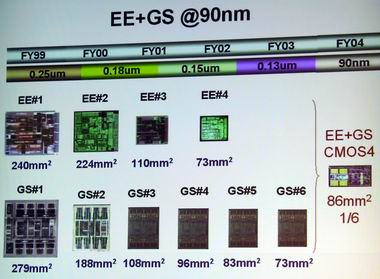

積極的な半導体設備投資はPS2のおかげ

PS2向けプロセッサとして1999年に発表された時のEEは、250ナノプロセスで240平方ミリという非常に大きなチップだった。それが毎年シュリンクを重ねて、現在は150ナノプロセスで73平方ミリメートルまで小型化した。同様に、当初279平方ミリメートルの大きさだったGSも、現在は130ナノプロセスで73平方ミリメートルになった。このような製造プロセスの微細化とチップの小型化によって、PS2の大幅なコストダウンと大量生産が可能になったのだ。その間の設備投資は、総額3000億円にも及ぶ。

PS2コアのシュリンクの歴史

「PS2は今年初頭に5000万台を出荷した。製造プロセスのシュリンクと新技術導入がコストダウンに貢献するというのは予測できるのだが、ボリュームアプリケーションがないと実現は難しい。PS2ような巨大な出荷スケールという“稀なケース”があったからこそ、積極的な設備投資もできた。今後は、コンピュータエンタテインメントシステム(ゲーム機)とデジタルCE機、ネットワークアプリケーションが融合していく時代。今回の投資でこの流れを推進していきたい」(久夛良木社長)。

関連記事

関連リンク

[西坂真人, ITmedia]

Copyright © ITmedia, Inc. All Rights Reserved.