第3回 Coreマイクロアーキテクチャ に迫る[後編]:新約・見てわかる パソコン解体新書(2/4 ページ)

オンライン版「見てわかるパソコン解体新書」の第3回目は、インテルのCoreマイクロアーキテクチャに迫ります。

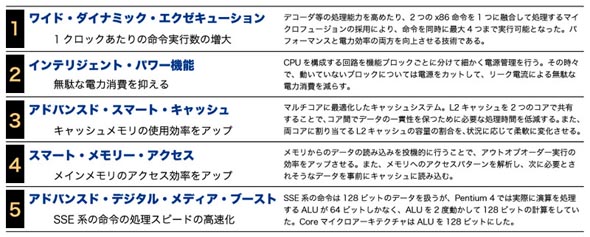

5つのイノベーション

インテルは、Coreマイクロアーキテクチャには5つのイノベーション(技術革新)があると言っています。その概要を次の表にまとめてみましたが、これらによって、Core 2 Duoの高いIPC値と優れた電力効率が実現されるわけです。

Core 2 Duo以前のPentium MなどのCPUですでに採用していた技術も含まれているので、イノベーションというのは少々大げさな気もします。それでは、5つの技術を1つずつ解説していきましょう。

ワイド・ダイナミック・エクゼキューション

要するに、1クロックあたりの同時実行命令数を多くするための技術で、マイクロフュージョン、マクロフュージョン、専用スタックエンジンの3つの技術が含まれています。これらこそ、Coreマイクロアーキテクチャのターボチャージャー。強制圧縮により、大量の命令をアウトオブオーダーエンジンに押し込むのです。説明しましょう。

1.マイクロフュージョン

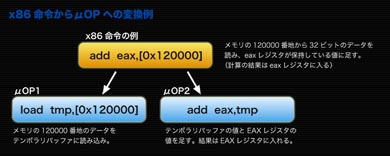

複雑なx86命令を単純な複数のマイクロOPに変換して処理することは、スーパースケーラやアウトオブオーダー機能を採用するために必要なことでした。しかし、処理すべき命令数が増えてしまうという問題もあります。

マイクロフュージョンとは、1つのx86命令から生成された2つのマイクロOP命令を、1つのマイクロOPに融合するというものです。store系の命令(メモリへの書き込み命令)と、load and op系の命令(メモリからのデータ読み込みを伴う演算命令)がその対象となります。

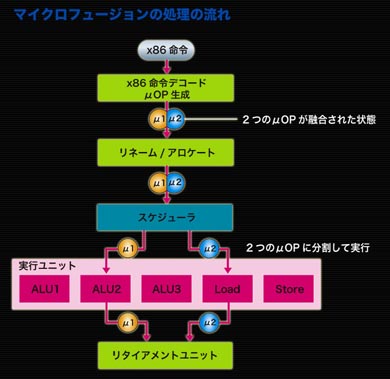

上の図のように、マイクロフュージョンされたマイクロOPは単独の命令としてパイプラインの中を流れて行き、デコード、リネーム、アロケートなどの処理が行われます。そして、ディスパッチユニットで2つのマイクロOPに分解されて、実行可能なものから実行ユニットに送られ、実行されることになります。両方のマイクロOPの実行が完了したら、リタイアメントユニットで命令のリタイア処理が行われます。マイクロフュージョンの採用によって、アウトオブオーダーの論理回路が処理するマイクロOPの数を10%ほど削減できるそうです。減った分だけ、ほかのマイクロOPを実行する余裕が生まれますから、パフォーマンスが向上します。また、従来2つのマイクロOPとして分散処理していた部分が1つの処理にまとめられるので、電力効率もアップします。

マイクロフュージョンについて、インテルは次のように説明しています。

『これは、タクシー待ちの乗客を 1 度に何人も乗車させることで、時間とエネルギーを節約することに似ています。』

なかなかうまい例えだと思います。

なお、マイクロフュージョンはPentium Mから使われている技術です。

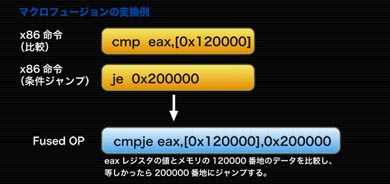

2.マクロフュージョン

マイクロフュージョンと1文字違いで紛らわしいので注意してください。あちらは「マイクロ」こちらは「マクロ」です。マクロフュージョンは、マイクロフュージョンと同様の命令融合を、x86命令レベルで行います。この融合が行われるのは、プログラム中に次のように比較命令と条件分岐命令が並んでいる場合です。

ご覧のように、2つのx86命令が、1つのマイクロOPに変換されます。そしてこのマイクロOPは、後で再分解されることなく、1つの実行ユニットで1サイクルで実行されるのです。そのために、特別に強化された実行ユニットを実装しています。

演算命令と条件ジャンプの組み合わせは、普通のプログラム中で非常に頻繁に登場するので、マクロフュージョンの効果は大きいはずです。

マクロフュージョンは、Coreマイクロアーキテクチャで初めて使われる技術です。

3.専用スタックエンジン

これを理解するには、スタックというものを理解しておく必要がありますが、詳しく説明するとかなり長くなってしまうので別の機会にゆずり、ここではごく簡単な説明だけにしましょう。

x86命令の中には、CPU内で処理中のデータを一時的にメモリに退避したり、逆にメモリから復帰させる、スタック命令というものがあります。スタック命令は、データをメモリに退避/復帰させるマイクロOPと、スタックポインタ(ESP)の値を増減するマイクロOPに分解され、実行ユニットで処理されます。

Coreマイクロアーキテクチャでは、スタックポインタの増減は専用の回路によって処理するようになっていて、そのためのマイクロOPは生成されません。スタック命令も非常に頻繁に使われるものであるため、これによってパイプラインに投入されるマイクロOPの数が5%程度削減されるそうです。結果として、処理速度と電力効率がアップします。

なお、専用スタックエンジンはPentium Mから使われています。

インテリジェント・パワー機能

Core 2 Duoは3億近いトランジスタで構成されたLSIで、その回路は無数の機能ブロックからなっています。全てのブロックが常に作動しているということはなく、そのときどきで働いていないブロックが多数あります。そこで、この動いていないブロックへの電源供給をこまめに停止して、無駄なリーク電力をカットしようというのがインテリジェント・パワー機能です。回路の状態を保持しつつ回路への電源供給を停止し、必要になったときに瞬時に電源を投入して回路を元の状態に復帰できる、パワー・ゲーティング技術を応用しています。

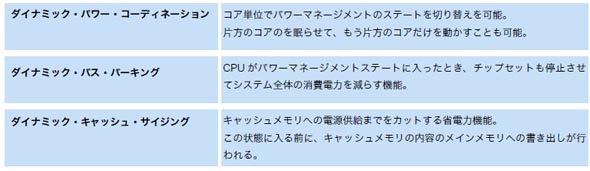

Core 2 Duoのうち、モバイルPC向けのTシリーズにだけ採用されているパワー・マネージメント機能については次の表を見てください。

Copyright © ITmedia, Inc. All Rights Reserved.