JEDECが「HBM3」の仕様書を公開 転送速度は毎秒819GBに

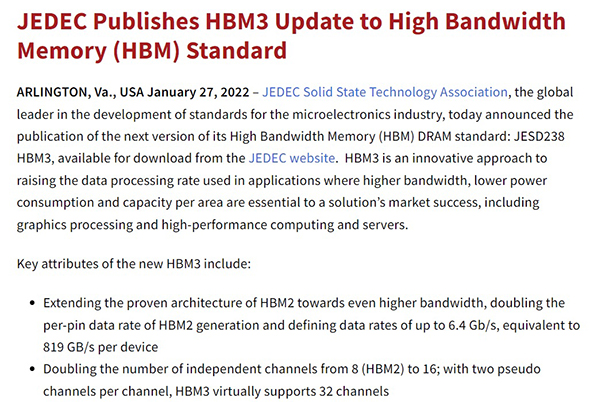

メモリの規格を策定する業界団体であるJEDECは1月27日(米国東部時間)、次世代のメモリである「HBM3(High Bandwidth Memory 3)」の仕様書を公開した。

メモリの規格を策定する業界団体であるJEDECは1月27日(米国東部時間)、次世代のメモリである「HBM3(High Bandwidth Memory 3)」の仕様書(JESD238)を公開した。HBMは広帯域、低消費電力で、実装面積が狭いところでも比較的大容量を確保できることから、GPUやハイパフォーマンスコンピューティング(HPC)での使用例が多い。またIntelは、次世代Xeonである「Sapphire Rapids」のラインアップに、HBMを内蔵した製品を用意する予定となっている。

HBM3では、データ転送速度を1ピン当たり毎秒6.4Gbpsに引き上げた。これはHBM2の2倍に当たる。この結果、メモリデバイスごとのデータ転送速度は毎秒819GBまで上がった。チャネル数もHBM2の8チャネルから倍の16チャネルに引き上げた。1チャネルを2本の疑似チャネルとして扱えるため、合計で32の疑似チャネルを使える。

HBMの特徴であるTSV(Through Silicon Via:シリコン貫通電極)を利用した積層メモリについては、4層、8層、12層に対応し、将来は16層まで対応する。1層当たりのメモリ容量は8Gbitから32Gbitまで対応。メモリデバイスごとの容量は4GB(8Gbitを4層)から64GB(32Gbitを16層)まで実現できる。

エンタープライズ用途で使用する企業から要望が多い、RAS(Reliability、Availability、Serviceability:信頼性、可用性、保守性)も強化した。「Symbol-Based ECC」という誤り訂正符号の機構をダイ上に実装した他、リアルタイムのエラーレポート機構も搭載した。消費電力の削減も進め、信号の振幅を小さくし(0.4V)、1.1Vで動作する。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

スーパーコンピューターの世界的なイベント「ISC 2021」に合わせて、IntelがHPC(ハイパフォーマンスコンピューティング)に関する取り組みを発表した。その中で、次世代のXeonスケーラブルプロセッサ(開発コード名:Sapphire Rapids)にHBM(広帯域メモリ)を内蔵するバージョンが用意されることが明らかとなった。 大解説! “Fiji”と“HBM”と“Fury”の先進性を知る

大解説! “Fiji”と“HBM”と“Fury”の先進性を知る

GeForce GTX 980 Tiに“迫る”パフォーマンスを実現したAMDの“Fiji”世代のGPUに導入した、将来を先取りしたという新機能とは。 「Zen」とHBMで大きく変わるAMDのCPUとGPU

「Zen」とHBMで大きく変わるAMDのCPUとGPU

AMDはCPUロードマップを大幅に変更。開発の主軸をハイパフォーマンスモデルへとシフトする。GPUとARMベースプロセッサも開発計画を大きく変えた。 HBMを導入するとこんなにコンパクト──AMD、Fijiの実物を日本で公開

HBMを導入するとこんなにコンパクト──AMD、Fijiの実物を日本で公開

Radeon R9 Fijiの登場を記念したユーザーイベントが秋葉原で開催。グラフィックスメモリをGPUに統合したFijiのすごさを日本のユーザーにアピールした。 AMD、HBM採用の“Fiji”世代GPU「Radeon R9 Fury」シリーズをE3で発表

AMD、HBM採用の“Fiji”世代GPU「Radeon R9 Fury」シリーズをE3で発表

出荷開始は6月24日から。液冷ユニットを搭載した最上位モデル「R9 Fury X」や6インチとコンパクトサイズの「R9 Fury Nano」などが登場する。