| News | 2003年2月21日 08:38 PM 更新 |

Intel、矢継ぎ早の新技術投入でサーバの技術革新を加速

IDFの3日目はエンタープライズ系にフォーカスした基調講演が行われ、XeonやItanium 2、サーバ系チップセットの最新ロードマップを公開。PCI Expressへの移行スケジュールなどについても言及された

「Intel Developer Forum Spring 2003」の3日目は、エンタープライズの分野にフォーカスした基調講演が行われ、上級副社長兼エンタープライズプラットフォームグループジェネラルマネージャーのMike Fister氏がサーバ分野を担当した。

Mike Fister氏

サーバ分野はデュアルプロセッサシステム用IA-32プロセッサにおいて、今年前半に3.06GHz版Xeonを、今年第3四半期に1Mバイトキャッシュ統合版Xeonを、それぞれ発表する。そして第4四半期には90ナノメートルプロセスの次世代Xeon(1Mバイトキャッシュ搭載のNocona)がローンチするスケジュールとなっている。

また4プロセッサ以上を搭載するシステム向けには来年前半に4Mバイトキャッシュ版(現行は最大2Mバイト)を、来年後半に90ナノメートルプロセスを採用した“Nocona”と、それに対応する新しいプラットフォームへと移行する。Fister氏はラージキャッシュ版の優位性をデモンストレーションするため、4プロセッサのSMPシステムと2プロセッサ×2ノードクラスタのシステムでSAPを動かし、パフォーマンスを比較して見せ、4プロセッサシステムの方が2倍以上高速との結果を見せた。

またIA-64を採用するシステムは今年、昨年の2倍の製品が各社から投入される見込みという。Fister氏によると、これまでIA-64はエンジニアリング用途で使われることが多かったが、今年からは本格的にビジネス向けのサーバとして採用が広がっていくはずと予測する。同時にItanium 2(McKinley)を32個搭載するNECの「Express 5800/1320Xc」が、ノンクラスタシステムとしては最高となる43万3100tpmCを達成したことをアナウンスした。

Itanium 2は現在、0.18ミクロンプロセスで製造される3Mバイト3次キャッシュメモリ1GHz動作のMcKinleyだが、年内には0.13ミクロンプロセスで6Mバイト3次キャッシュメモリ1.5GHz動作のItanium 2(Madison)に置き換わり、来年にはそれが9Mバイト、1.5GHz以上へと進化する。さらにMadisonと同じコアアーキテクチャを持ち、消費電力が半分となるDeerfieldと呼ばれる低電圧バージョンが用意される。

低電圧Itanium 2は消費電力が62ワットで動作速度は1GHz、3次キャッシュメモリは1.5Mバイト、デュアルプロセッサ用にデチューンされ、より小型のサーバやワークステーションで採用される見込みだ。消費電力が下がったことで、従来よりも小さな筐体にもシステムを収めることが可能になった。

コンパックが開発中のRX2600。パーティショニング機能を持ち、Itanium2とPA-RISC、両方のシステムボードを混載可能なハイエンドサーバ

Itanium2の90ナノメートルプロセス版は2005年。コードネームは“Montecito”で、1つのプロセッサコアとより大きなキャッシュメモリと2個のプロセッサコアを搭載するマルチチップモジュール(1つのLSIパッケージに複数のダイを実装したモジュール)になる。

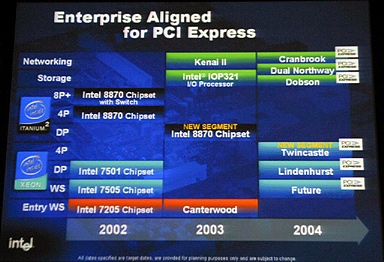

Fister氏はサーバシステムのI/O技術についても言及。Intelはすでにサーバ分野でもシリアル技術のPCI Expressに移行することを表明している。サーバ分野におけるPCI Expressの導入は2004年後半を予定。現在のPCI-XからPCI Expressに移行することで、マザーボード上に占める配線面積は53%削減され、ブリッジチップが不要になることで3チップが削減可能。サーバシステムのローコスト化、信頼性強化を進めることができる。

サーバ・ワークステーション向けチップセットのロードマップ

またPCI Expressの導入と共に、イーサネットも現在のギガビットイーサから、10ギガビットイーサへと移行する。来年はサーバ向けチップセットでもシリアルATAが実装され、サーバの中からもパラレル技術がほぼ無くなる状況になりそうだ。

Fister氏は「次世代の性能を備える、標準化されたさまざまな技術が出荷を控えている。われわれは、それら標準技術を基礎としたシステム構成要素を提供することで、顧客に対して革新的な性能を短期間で提供できる」と、今後投入予定の製品への期待を煽った。

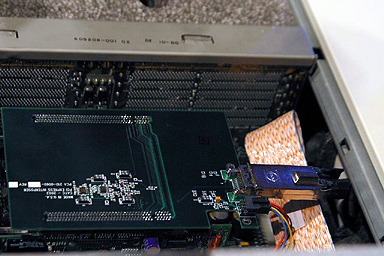

また基調講演ではPCI Expressが実際に稼働しているところをデモンストレーション。2リンクで接続された2つの機器間でデータを転送するデモを行った。1リンクの速度は毎秒187Mバイトで、トータルの帯域は毎秒400Mバイトに迫る。

2リンクで毎秒400Mバイト近い帯域で繋がるデモが行われたPCI Expressの評価ボード

関連記事

富士通と米Intelが、ミッションクリティカル分野向けのLinux対応IAサーバ開発で協業すると発表。同日行われた会見では、協業で開発する高性能Linux-IAサーバについて両社幹部が語った

Itaniumのリリーススケジュールに、これまでロードマップになかった“Madison II”が加わった。9MバイトL3キャッシュ搭載のMadisonだ。またデュアルコアItaniumは当初の計画より早く、2005年にリリースされる

Intel Technology Groupが、同部門に関わるさまざまな技術の最新動向について説明を行った。PCI Express、UPnP、Serial ATA、Advanced TCAといった、注目の次世代標準技術のステータスは今、どうなっているのだろうか

関連リンク

[本田雅一, ITmedia]

Copyright © ITmedia, Inc. All Rights Reserved.