通信インフラでの利用を想定 Intelが新型「Xeon Dプロセッサ」を投入:最大100GbE内蔵

エッジコンピューティングを含む通信インフラ機器での利用を想定した「Xeon Dプロセッサ」がモデルチェンジした。CPU部分はIce Lakeアーキテクチャベースとなり、CPU直結のPCI Express 4.0バスも用意される。

Intelは2月24日(米国太平洋時間)、産業向けの新型SoC(System-On-a-Chip)「Xeon D-1700プロセッサ」「Xeon D-2700プロセッサ」を発表した。SDN(ソフトウェア定義の通信ネットワーク)のハードウェアでの活用やエッジサーバでの利用を想定した製品で、搭載製品は順次登場する予定だ。

Xeon D-1700/2700プロセッサの概要

Xeon D-1700/2700プロセッサのCPU部分は、先行して発売された第3世代XeonスケーラブルプロセッサやXeon W-3300プロセッサと同様に10nmプロセスの「Ice Lakeアーキテクチャ」に基づいて設計されている。Intelによると、従来のXeon D-1600/2100プロセッサにおける同等クラス製品から以下の通りの高速化を図っているという。

- ビジュアルの推論処理速度(最大2.4倍)

- ネットワーク上の複雑なワークロード(※1)の処理速度(最大1.7倍)

- SD-WAN、SASE、IPsecのエッジ処理における処理速度(最大1.5倍)

- アプリケーション配信コントローラーやTLSを使ったセキュリティ機器の処理速度(最大1.8倍)

- 通信機器の処理速度(最大1.56倍)

(※1)5Gにおけるエッジ側でのUPF(ユーザーから送受信されるデータを処理する機能)を想定

Xeon D-1700プロセッサは「スタンダードパッケージ」という位置付けで、約45mm四方のFCBGAパッケージで提供される。コア数はモデルによって2〜10基となる。TDP(熱設計電力)はモデルによって25〜85Wと幅がある

Xeon D-2700プロセッサは「アドバンストパッケージ」という位置付けで、約52.5×45mmのFCBGAパッケージで提供される。コア数はモデルによって4〜20基となる。TDPはモデルによって64〜125Wと幅がある

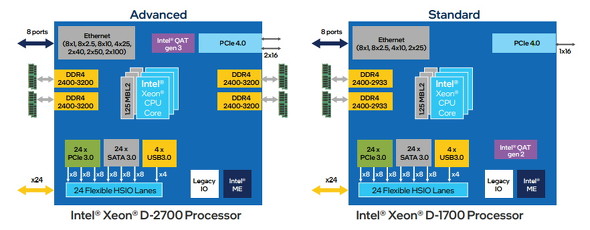

メインメモリはDDR4規格に対応し、最大チャネル数はXeon D-1700プロセッサでは2または3(モデルによる)、Xeon D-2700プロセッサでは4となる。CPU直結のPCI Express 4.0バスも備えており、Xeon D-1700プロセッサでは16レーン×1、Xeon D-2700プロセッサでは16レーン×2(合計32レーン)を利用できる。PCI Express 3.0バスはFlexible HSIO(High-Speed I/O)経由で最大24レーンを確保可能だ。

両プロセッサは8ポート分のEhternet(有線LAN)インタフェースも統合しており、最大50Gbpsまたは100Gbpsのスループット(実効通信速度)で通信できるようになっている(最大スループットはモデルによる)。

その他の入出力ポートは主に以下のものを備えている(★印が付いているものはFlexible HSIO経由で提供)。

- Serial ATA 3.0ポート(最大24ポート)★

- USB 3.0ポート(最大4ポート)★

- eMMC 5.1バス

- USB 2.0ポート×2

Xeon D-2700プロセッサ(左)とXeon D-1700プロセッサ(右)の構造図。Flexible HSIO経由で提供されるレーン/ポートの合計数は最大24となる。ただし、Flexible HSIOの合計帯域(通信速度)は、PCI Express 3.0 x16相当となることには留意したい

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

デスクトップワークステーション向け新CPU「Xeon W-3300」登場 最大38コアでPCI Express 4.0は64レーン用意

デスクトップワークステーション向け新CPU「Xeon W-3300」登場 最大38コアでPCI Express 4.0は64レーン用意

Intelが、サーバ/データセンター向けに続いてデスクトップワークステーション向けにも新しいXeonプロセッサを投入する。Ice LakeアーキテクチャベースでAI処理を高速化したことが特徴で、Coreプロセッサと比較するとハイエンド用途でも使える改良が施されている。 Intelが「第3世代Xeonスケーラブルプロセッサ(Ice Lake)」を発表 最大40コアで処理能力を向上

Intelが「第3世代Xeonスケーラブルプロセッサ(Ice Lake)」を発表 最大40コアで処理能力を向上

Intelが、Ice Lakeアーキテクチャに基づく第3世代Xeonスケーラブルプロセッサを発表した。クロック当たりの処理性能を向上し、機械学習ベースのAI処理も高速化している。なお、既存のCooper Lakeアーキテクチャの製品は継続販売(併売)される。 Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

スーパーコンピューターの世界的なイベント「ISC 2021」に合わせて、IntelがHPC(ハイパフォーマンスコンピューティング)に関する取り組みを発表した。その中で、次世代のXeonスケーラブルプロセッサ(開発コード名:Sapphire Rapids)にHBM(広帯域メモリ)を内蔵するバージョンが用意されることが明らかとなった。