そのあふれる自信はどこから? Intelが半導体「受託生産」の成功を確信する理由【中編】(2/3 ページ)

Intelが、半導体の受託生産事業「Intel Foundry」を本格的にスタートした。受託生産事業者(ファウンドリー)としては新参者でありながら、同社は既に自信満々のようである。それはなぜなのか、ちょっと深掘りして考察していこうと思う。

異なる“ダイ”をつなげる技術を豊富に持つIntel

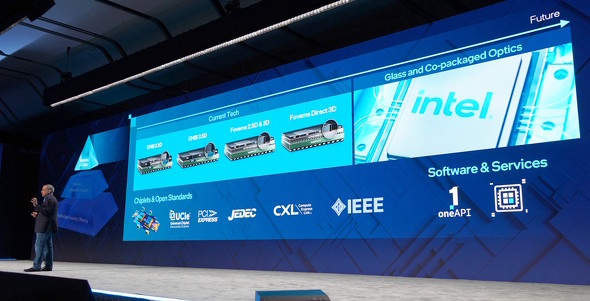

今回の発表では、Intel Foundryにおいて提供できるACPは現時点で6種類あるという。

1つ目は、ダイをインターポーザー基板にパッケージ化する、通常のパッケージスタイルである「FCBGA 2D」だ。2つ目は、FCBGA 2Dを拡張して、ダイとインターポーザー基板の間に、高密度中間基板(パッチ)を挟んでパッケージ化する「FCBGA 2D+」だ。これは、かつてXeonプロセッサの製造に活用されていたこともある。

3つ目は「EMIB 2.5D」だ。EMIBとは「Embedded Multi-die Integrated Bridge」の略で、平面方向に並べた複数のダイを、インターポーザー基板を介して接続するパッケージスタイルだ。Intel Foundryの顧客に対しては第二世代EMIBと呼ばれる、55μm〜45μmのバンプピッチでのEMIB 2.5D技術が提供されるという。4つ目は「EMIB 3.5D」だ。これはEMIB 2.5Dの拡張版ともいえる技術で、複数のダイをインターポーザー基板ではなく、後述する「Foveros」を用いてベースダイを介して接続する。

5つ目は「Foveros 2.5D&3D」だ。これは以前は「Foveros Omni」と呼ばれていた技術で、重ね合わせた2つのダイを、要所では最短距離で接合し、必要であればインターポーザー基板に接続するなどするパッケージスタイルだ。ダイ間接合には「TSV(Through-Silicon Via)配線」が用いられ、インターポーザー基板への接続にはマイクロバンプ接続が使われる。

そして6つ目は「Foveros Direct 3D」だ。重ね合わせた複数のダイを、ダイ上に形成した銅電極を使って熱圧着させるという、Intelが誇る最先端パッケージ技術となる。この技術のポイントは、切り出された単体ダイ同士を接続するのではなく、ウエハ“全体”を相互に直接接合するという点にある。接合技術の歴史を見てきた人間からすると、結構驚きのある技術でもある。接合ピッチは第1世代では9μmだったものが、第2世代ではわずか3μmに短縮されている。これまたビックリするほどの微細化だ。接合されたダイ同士は、超広帯域かつ超低遅延での相互接続が可能となる。

Intelが提供する、高度なチップレットパッケージング技術は、絵空事ではない。その多くは、既に自社CPUの製造で実績を積み重ねられてきたものである。

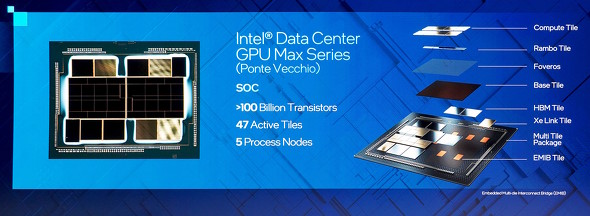

パン氏は、その証拠/象徴として2022年9月に発表されたデータセンター向けGPU「Intel Data Center GPU Max」シリーズ(開発コード名:Ponte Vecchio)を挙げる。

Intel Data Center GPU Maxシリーズは、5つの異なるプロセスノードで製造した合計47基ものダイを1パッケージにまとめ、トランジスタ総数1000億のGPUとして動作させている。この偉業は、真に“偉業”といえる。

Intel Data Center GPU Maxシリーズは、47基のチップレット(ダイ)を1パッケージに集約した超大規模GPUとなっている。Intel Foundryは、この規模のプロセッサを製造できる技術力があるということを意味する

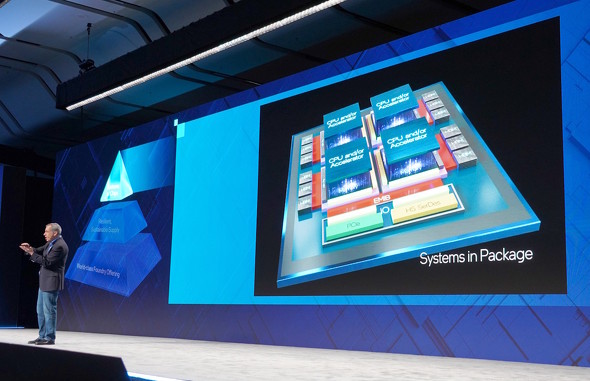

パン氏はここまでを総括し、「モノシリック(単一の)ダイで高機能かつ高性能なプロセッサの製造する時代は、そろそろ終焉(しゅうえん)を迎える。これからは『System of Chips』の時代へと突入していくのだ」と語った。

これまでの「SoC」といえば、「コンピュータを構成する複数のロジック(回路)を1チップに集約した統合プロセッサ」の意である「System on a Chip」の略だったが、Intel Foundryで作れるSoCは「System of Chips」(複数のシステムを集約化した統合プロセッサ)とでも言いたそうだ。

Intel Foundryでは、単一ダイのプロセッサだけでなく、複数のダイを1つに集約して「Systems in Package」を製造できるというメッセージ。そのまま「SiP」と略しても良さそうだが、「SoC」という略を「System of Chips」という意味でリプレースしても良さそうな気もする

ここまで来ると、最初はピンとこなかった「世界初の『システム・ファウンドリー』になった」という発言の言わんとするところが見えてくる。Intel Foundryは半導体受託事業であると同時に、高度なパッケージング受託業者でもあると言いたいのだ。

そして「ファウンドリー」の前に、わざわざ「システム」と付けたのは、高度なパッケージング技術が幾つもの自社製プロセッサの量産で実用化済み、あるいはテスト製造で実用に問題ないことが確認されていて、それを顧客に“即”提供できることを強調する狙いがある。

確かに、今のところここまでできる体制が整っているのは、半導体業界を見渡してもIntelだけかもしれない。

1つ、心配な要素を挙げるとすれば、Intel Foundryは「超高度なアーキテクチャのプロセッサを製造したい顧客向け」の受託生産サービスになってしまう可能性が高いことだろう。ただし、昨今のAIブームでそのようなプロセッサへのニーズが高まっていることもあって、当のIntelはそこまで不安に思っていないようだ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

2030年までに“世界第2位”を目指す! Intelが半導体の「受託生産」に乗り出す理由【前編】

2030年までに“世界第2位”を目指す! Intelが半導体の「受託生産」に乗り出す理由【前編】

Intelの半導体受託生産事業「Intel Foundry」が本格的に始動した。研究/開発から生産まで一貫して行う垂直統合体制だった同社が、ここに来て受託生産(ファウンドリー)事業に注力し始めたのはなぜなのだろうか。この記事では、その動機(モチベーション)について考察していきたい。 IntelがAI時代を見据えた半導体の「受託生産」ロードマップを発表 2030年までに世界第2位を目指す

IntelがAI時代を見据えた半導体の「受託生産」ロードマップを発表 2030年までに世界第2位を目指す

Intelが、半導体の受託生産(ファウンドリー)サービスに関するイベントを開催した。その中で、 ついに! ようやく? 「Intel Maxシリーズ」2023年1月から出荷 HBM付き「Xeon Max」と高密度実装GPU「Intel GPU Max」

ついに! ようやく? 「Intel Maxシリーズ」2023年1月から出荷 HBM付き「Xeon Max」と高密度実装GPU「Intel GPU Max」

Intelが、HPC(ハイパフォーマンスコンピューティング)と機械学習ベースのAI(人工知能)用のCPU/GPUの統一ブランドとして「Intel Max」を立ち上げる。その第1弾製品はSappire Rapidsと呼ばれていたCPU「Xeon Maxプロセッサ」と、Ponte Vecchioと呼ばれていた「Intel Data Center GPU Max」である。 IntelとMediaTekがファウンドリー事業でパートナーシップを締結 IntelがMediaTekのチップを製造

IntelとMediaTekがファウンドリー事業でパートナーシップを締結 IntelがMediaTekのチップを製造

IntelとMediaTekがファウンドリー事業でのパートナーシップ締結を発表した。2021年7月には、Qualcomm向けのプロセッサ製造を発表済みだ。 2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

Intelが半導体生産のロードマップを説明するイベントを開催した。2022年には7nmプロセスの製品が、2024年には新技術を取り入れた製品が登場する見通しだ。