次世代CPU「Lunar Lake」でIntelが目指す“AI PC”とは? 驚くべき進化点と見える弱点、その克服法(2/4 ページ)

COMPUTEX TAIPEI 2024に先立って、Intelが今後発売される予定のCPUに関する技術説明会を開催した。この記事では、2024年第4四半期に登場する予定のモバイル向けCPU「Lunar Lake」(開発コード名)の技術的概要を紹介する。

Pコアでハイパースレッディング廃止 今後のCPUにも影響するか?

Lunar LakeのComputeタイル(CPUコア)は、高性能コア(Pコア)が4基、高効率コアが4基の計8コア構成となる。第12世代以降のIntel CPUのノリで考えると、「ということは合計8コア12スレッドなのかな?」と思ってしまう。

しかし、このLunar LakeではPコアがマルチスレッド動作(SMT)、Intel風にいうと「ハイパースレッディング」に対応していない。つまり8コア8スレッドのCPUということになる。

「なぜハイパースレッディングを廃止してしまったの?」という疑問に対する詳細は、別の記事で解説したいと思っている。しかし、読者の皆さん的には関心が高いと思うので、本稿でも簡単に説明したいと思う。

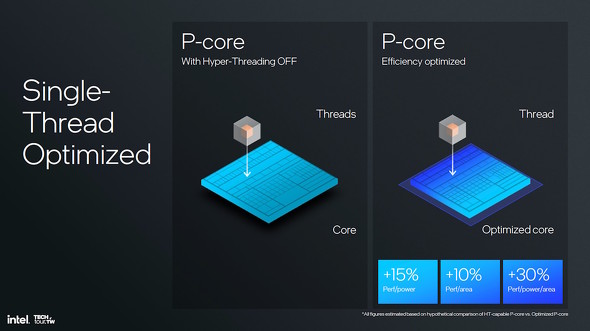

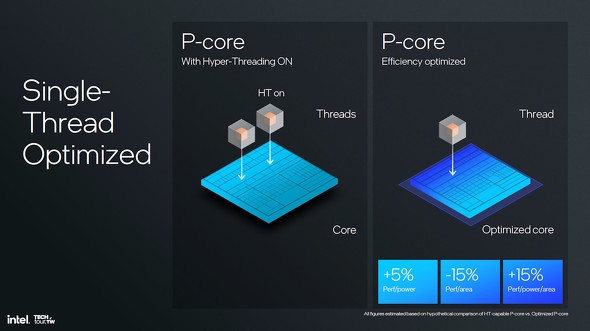

結論からいうと、「Pコアにおけるハイパースレッディング廃止」という方策は、「機能面での妥協」ではなく、「現状では引き出せる性能と消費電力のバランスを最適化しやすい」という理由から導き出された。

つまり、微細化が進んだ現状までのプロセスノードにおいて、ハイパースレッディング機能を実装するために必要なトランジスタ数と、これらを動かすための消費電力、そしてハイパースレッディングによって得られるパフォーマンス向上率のバランスが割に合わなくなりつつあるのだ。

CPUを始めとする各種プロセッサに「ある機能」を実装するためには、プロセッサダイにおいて、一定の面積を専有して、機能を実現するための「トランジスタロジック」を形成しなくてはならない。通常、その面積占有率はトランジスタの数と比例するため、消費電力の増大に直結する。

特にハイパースレッディングの実装に当たっては、演算器のセットはCPU1基分でも、「レジスタファイル群」、命令実行用の「キューイングバッファ」や「スケジューリング機構」は2基分必要となる。これらがあるがゆえに、SRAMロジックの占有面積はどうしても大きくなってしまう。

最近のCPUでは、パフォーマンスの向上率を「IPC(1クロックあたりの命令実行数)」で算出することが多いが、ハイパースレッディングはまさにIPCを向上するために生まれた技術だ。

Intelが「Pentium 4」で初めてハイパースレッディングを実装したのは2002年。当時は「シングルスレッドにおけるIPCを向上させる」よりも、「互いに独立した無関係な2スレッドを並列実行させる」ハイパースレッディングの方が、全体としてのIPCを向上しやすかった。しかし、時代が流れて技術が進歩すると、シングルスレッド処理のために盛り込まれたIPC向上の仕組み(順不同のスーパースカラ実行/条件分岐予測精度の向上)が、ハイパースレッディングで得られるIPC向上効果と大差ない状況となった。

要するに、昨今はハイパースレッディング機構の搭載によって、トランジスタや消費電力が増える代わりに得られるメリットが薄くなったのである。

むしろ、ハイパースレッディング処理に伴い生じるオーバーヘッド(レジスタファイルの総入れ替えなど)が、シングルスレッドのパフォーマンスを阻害するケースも出てきている。特にゲームアプリのコアプログラムは、逐次処理の塊であるためシングルスレッド性能がパフォーマンスを左右することが多いので、Pコアのマルチスレッド非対応化はむしろ歓迎されるだろう。

もっと極端にいえば、「ハイパースレッディングに対応させるくらいなら、Eコアを増やした方がマシなんじゃね?」という状況なのである。

ハイパースレッディングの実装によって増えるトランジスタの数だが、先に触れたPentium 4の場合が「1コアあたりプラス5%」程度だった。しかし、近年のCPUではこれが「1コアあたりプラス10〜20%」程度にまで達している。

EコアのサイズがPコアの4分の1程度にとどまることを考えると、「面積を考えてもEコア増やした方がいいよな、そうだよな!」的な状況になっているのだ。

仮にこのCPUコアでハイパースレッディングを有効化してマルチスレッド処理を行ったとすると、IPCの向上は15%にとどまる。「それならハイパースレッディングを非対応とすることで、浮いたトランジスタのスペースと消費電力を別のことに使おう」と考えたのが、今回のLunar LakeのPコアなのだ

今回のイベントの質疑応答において、Intelは「サーバ向けCPUにはなら、面積と電力のバジェット(予算)をある程度多く取ることをためらわない設計ができるので、ハイパースレッディングを引き続き搭載するかもしれない」と語った。

少し遠回りな表現にも思えるが、この言い方から察するに、優れた省電力性能と絶対的なシングルスレッド性能を追求する観点から、クライアント向けCPUではハイパースレッディング機構を順次なくしていく可能性は高い。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Intelのモバイル向け次世代CPU「Lunar Lake」は2024年第3四半期に登場 ライバルを超えるAI処理パフォーマンスを実現

Intelのモバイル向け次世代CPU「Lunar Lake」は2024年第3四半期に登場 ライバルを超えるAI処理パフォーマンスを実現

Intelが、モバイル向け次世代CPU「Lunar Lake」の概要を発表した。2024年第3四半期に登場する予定で、ライバルCPU/SoCよりも高速なAIパフォーマンスを発揮できることが特徴だ。 「AI PC」がベールを脱ぐ! 次世代のモバイル向け「Core Ultraプロセッサ」正式発表 搭載ノートPCは順次発売

「AI PC」がベールを脱ぐ! 次世代のモバイル向け「Core Ultraプロセッサ」正式発表 搭載ノートPCは順次発売

Intelが発表を予告していた「Core Ultraプロセッサ」が、ついに正式発表された。全てのモデルにAIプロセッサ(NPU)を搭載しており、NPUを利用できるアプリのパフォーマンスが大きく向上することが特徴だ。 さよなら「i」 こんにちは「Ultra」――Intel Coreプロセッサが15年ぶりにリブランディング Meteor Lakeから適用

さよなら「i」 こんにちは「Ultra」――Intel Coreプロセッサが15年ぶりにリブランディング Meteor Lakeから適用

2023年後半に登場する新型CPU「Meteor Lake(開発コード名)」に合わせて、IntelがCoreプロセッサのリブランディングを実施する。モデル名に含まれる「i」を省く他、「第○世代」という表記を廃止することでブランドそのもののシンプル化を進める一方で、最先端モデルには新たに「Core Ultraプロセッサ」というブランドを導入するという。 Intelが次世代CPU「Meteor Lake」の概要をチラ見せ 全モデルに「AIエンジン」を搭載

Intelが次世代CPU「Meteor Lake」の概要をチラ見せ 全モデルに「AIエンジン」を搭載

Intelが「Meteor Lake(メテオレイク)」というコード名で開発を進めているCPUの概要情報を公開した。同社初の7nmプロセスCPUは、全モデルにCPUコアとは別体の「AIエンジン」を搭載するという。 2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

Intelが半導体生産のロードマップを説明するイベントを開催した。2022年には7nmプロセスの製品が、2024年には新技術を取り入れた製品が登場する見通しだ。