2025年末出荷開始予定の「Core Ultraプロセッサ(シリーズ3)」のCPUコア構造を“深掘り”(2/4 ページ)

Intelが2025年末に一部モデルを出荷する予定の「Core Ultraプロセッサ(シリーズ3)」(開発コード名:Panther Lake)だが、CPUコアを改良しているという。どう改良されているのか、解説しよう。

分岐予測の高速化

さらに、IntelによるとCougar Coveでは「分岐予測ユニット(BPU:Branch Prediction Unit)」の精度向上と遅延抑制も併せて行ったという。

競合のAMDとは対照的に、IntelはBPUのアルゴリズムを表向きに公開していない。そこで筆者は同社でCPU設計を担うスティーブン・ロビンソン氏(チーフCPUアーキテクト兼フェロー)にインタビューした際に「分岐予測アルゴリズムの詳細が非公開なら、ヒントだけでもください!」と聞いてみた。

ロビンソン氏は「我々のBPUは、基本的にはTAGE(テイジ)法を活用している」と答えた。どうやらPコアもEコアのどちらもTAGE法を使っているようだ。

……と、「TAGE法って何?」という人もいると思うので、CPUにおける命令分岐の予測アルゴリズムについて解説する。

CPUにおける命令分岐予測における最も基本的なアルゴリズムは、システム全体の分岐履歴データである「Global History Register(GHR)」と、特定アドレスにおける分岐履歴データである「Branch History Register(BHR)」を参照して、これらの情報をヒストグラム的な管理機構で制御するというものだ。

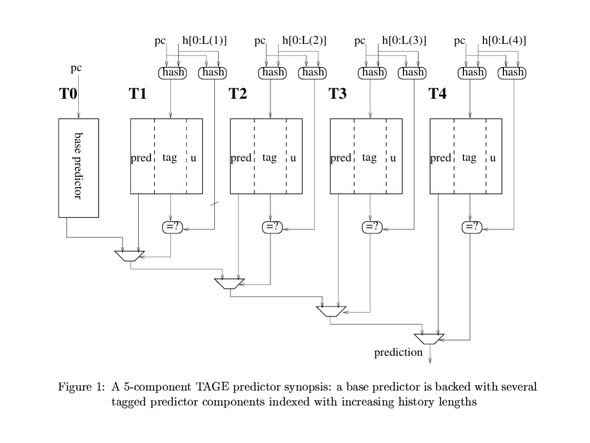

TAGE法は、先述の基本アルゴリズムにおける分岐履歴データをより高度に拡張したものだ。TAGEは「Tagged Geometric History Length」の略で、日本語ではそのまま訳した「タグ付き幾何学的履歴長」と呼ばれる。

TAGE法では、GHR的なグローバル分岐履歴情報を複数階層的に持ち,それぞれの階層が管理する分岐履歴の統計時間範囲を、幾何数列(Geometric Sequence)的に設定する。TAGEの「G」は、幾何数列を利用することに由来する。

「幾何数列って何?」っていうところだが、要するに「等比数列」のことだ。たてば「公比が2」であれば、階層が1段深い所では分岐履歴の統計時間範囲を「2倍」ずつ広げるような階層構造を取る。

タグ付き幾何履歴長分岐予測(TAGE)の概念図。この図は分岐履歴の統計時間の範囲を「4階層」で持ったタイプで、分岐予測システム全体ではベースとなる分岐予測器とは別に、4基の分岐予測器を備えることになる。一般的にTAGE法では、最も長い分岐履歴をつかさどる一番の奥の分岐予測器で“ヒット”したら、それを優先採択するようになっている(出典:A case for (partially) TAgged GEometric history length branch prediction)

ロビンソン氏は筆者の質問に対してこう答えた。

我々のTAGE法では、『複数長のグローバル履歴』『G-Tables』『ターゲットアレイ(Target Arrays)』を持つ、パスベースのインデックス(Path-based Index)を採用しています。特にインデックスの付け方を変更していて、数十バイトや数百バイトを一度に検索して、次に実行される分岐を探すことができます。

つまり、我々のBPUは高周波(≒局所ループ)/高容量/低遅延を実現しています。これは(分岐予測に)「パーセプトロン法」を採用する他社(※1)との大きな相違点にもなっています。

(※1)筆者注:言うまでもなくAMDのことである

手短ながらも、大きなヒントを含んだ回答だ。

ロビンソン氏のいう「複数長のグローバル履歴」は、「Geometric History Lengths(GHL)」、つまりTAGE法の基本方針である幾何級数(等比数列の総和)で表される履歴長を指す。後段に来るグローバル履歴ほど、統計時間範囲を長く記録していることになる。

「G-Table」は「履歴テーブル(History Tables)」を指している。グローバル履歴ごとに、その各履歴長に対応した「タグ付き予測テーブル群」のことだ。具体的には、分岐命令のプログラムカウンターアドレスなどを元にして生成した「タグ」と、分岐したか否かの「カウンター」、そして「補助パラメーター」などから成る。

恐らく、数百バイト級のウィンドウを一気に探索して、確度の高い分岐予測を超低遅延で見つける仕組みになっているのだろう。

Cougar Coveの最適化に関して説明した下のスライドを見てみると、分岐予測に関する説明は「パフォーマンスとエネルギー効率を改善」とだけあり、かなり漠然としている。

しかし先ほどのロビンソン氏の回答を踏まえると、Intelは遅延が大きくなるパーセプトロン法を使う他社(AMD)を意識して、低遅延性を重視したチューニングを行った――そう主張しているようにも思える。

さて、ロビンソン氏がいうところのターゲットアレイは、「Branch Target Buffer(BTB)」のことを指していると思われる。分岐予測が採用された場合には、タグと共にストアされている分岐先アドレスをBTBから取得し、実際にジャンプするという実装となる。

さらに、筆者はロビンソン氏の「パスベースのインデックスを採用」という言葉にも、パフォーマンス向上における重大なヒントが隠されていると考える。

分岐予測ユニットにおけるパスベースのインデックス化は、分岐予測でテーブルを引く「鍵(Index/Tag)」を作るときに、「分岐の結果履歴(分岐したか否か:Taken/Not)だけでなく、「どの分岐アドレス列を通って来たか」、つまり分岐経路(パス)に関する情報も混ぜる手法だ。狙いは、異なる状況が同じエントリーに重なる“衝突”(BPUの「エイリアシング現象」)の減少によって、分岐予測の精度を向上させるところにある。TAGE法では定番ともいえる、効果の大きい改善アプローチである。

TAGE法自体は、幾何履歴長や各種バッファサイズを変更することで、ある程度はスケーラブルの(規模に応じた)パフォーマンスを発揮する。そのため、PコアとEコアとでは設定を変えていると思われる。具体的には、Eコアの方はコンパクトに収めているはずだ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Intelの「Core Ultraプロセッサ(シリーズ3)」は2025年末に一部出荷 2026年1月にはラインアップを拡充

Intelの「Core Ultraプロセッサ(シリーズ3)」は2025年末に一部出荷 2026年1月にはラインアップを拡充

Intelが、「Panther Lake」という開発コード名で開発を進めていたCPUを新しいCore Ultraプロセッサとして発売することになった。2025年内に大量生産を開始し、同年末に一部製品の出荷を開始する見通しだ。2026年1月には、より広範な製品を集荷するという。 Intelの新型CPU「Core Ultraプロセッサ(シリーズ3)」は何が変わった? Lunar Lakeからの進化をチェック!

Intelの新型CPU「Core Ultraプロセッサ(シリーズ3)」は何が変わった? Lunar Lakeからの進化をチェック!

Intelが2025年末に出荷を開始する予定のPanther Lakeこと「Core Ultraプロセッサ(シリーズ3)」。その技術的特徴を数回に分けて解説する。今回は、全体的な概要を紹介する。 Intelが次世代CPU「Panther Lake」を“チラ見せ” 製品は2026年初頭に発売予定

Intelが次世代CPU「Panther Lake」を“チラ見せ” 製品は2026年初頭に発売予定

Intelが「Core Ultraプロセッサ(シリーズ2)」の次に投入する予定のCPU「Panter Lake」のデモンストレーションを行った。量産は2025年後半から始まる予定で、搭載製品は2025年初頭に発売される見通しだ。 Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが、VLSIシンポジウム2024に合わせて「Intel 3」の詳細を発表した。「Intel 4」の細かい部分を改良したプロセスだが、それが最大18%のパフォーマンス改善につながっているという。 「Core Ultraプロセッサ(シリーズ2)」は驚きの内蔵GPU性能に メモリ帯域が当初発表から“倍増”

「Core Ultraプロセッサ(シリーズ2)」は驚きの内蔵GPU性能に メモリ帯域が当初発表から“倍増”

IntelがLuna Lakeこと「Core Ultra 200Vプロセッサ」を発表した。Core Ultraプロセッサ(シリーズ2)のモバイル向けモデルという位置付けだが、どのような特徴があるのだろうか。ドイツ・ベルリンで開催された発表会で得られた情報をもとにまとめた。