2025年末出荷開始予定の「Core Ultraプロセッサ(シリーズ3)」のCPUコア構造を“深掘り”(3/4 ページ)

Intelが2025年末に一部モデルを出荷する予定の「Core Ultraプロセッサ(シリーズ3)」(開発コード名:Panther Lake)だが、CPUコアを改良しているという。どう改良されているのか、解説しよう。

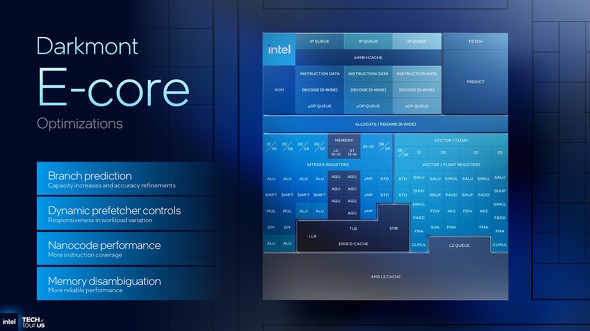

Eコア/LP Eコア「Darkmont」:Intel 18Aへの最適化がメイン

Panther Lakeの高効率コア(Eコア)と低消費電力Eコア(LP Eコア)のマイクロアーキテクチャは「Darkmont」(開発コード名)と呼ばれる。

x86コードをデコードして出力されるマイクロ命令の発行ポートは26基構成で、4コアで4MBのL2キャッシュを共有する仕様となっている。すぐに分かった人もいると思うが、フロントエンド部やキャッシュ回りの基本仕様は、Lunar Lake/Arrow Lakeで共通して使われた先代の「Skymont」(開発コード名)と大きく変わらない。

ブロックダイヤグラムを見ても、Darkmontになって大きく変わった所はない。PコアのCougar Coveと同様に、物理設計を「Intel 18A」プロセスに最適化したことが分かりやすい進化ポイントということになるだろう。

L1キャッシュは、コア1基あたり96KBだ。ブロックダイアグラムにも記載があるが、96KBの内訳は命令キャッシュに64KB、データキャッシュに32KBとなる。これも、Lunar Lake/Arrow Lakeから変わっていない。

しかし、Skymontから何も変わっていないかというと、そうでもない。PコアのCougar Coveと同じようにファインチューニングが施され、劇的ではないものの着実に性能を向上しているという。

先に掲載したDarkmontのブロックダイアグラムの左下に改良ポイントが箇条書きにされているので、順番に解説していこう。

Branch Predition(分岐予測)

1つ目の「Branch Predition(分岐予測)」の改善だが、特に「局所的なループ検出(Loop Stream Detection:LSD)」機能が進化している。

LSDは特別なループ動作モードで、極めて小さい局所ループを回すコードを自動認識して、命令キャッシュすら使わずにマイクロ命令キュー(ブロックダイアグラムで「μOP QUEUE」書かれている箇所)で直接ループ命令を実行するようになっている。バックグラウンドプロセスや入出力(I/O)処理に適した動作モードであり、まさしく“Eコアらしい”ものだ。

実はLSD自体は、Skymontで初めて実装された。Darkmontではこれを改良し、ループ周回時には「x86命令デコーダー」「命令キャッシュ」「分岐予測ユニット」といったフロントエンドユニットのほとんどを「クロック/電源ゲーティング」を使って“寝かせる”ことで消費電力を節約できるようになった。省電力状態でも、高いパフォーマンスを発揮できるようになったのだ。

Dynamic Prefetcherr Controls(動的プリフェッチ制御)

2つ目の「Dynamic Prefetcherr Controls」とは、命令のプリフェッチを動的に(自動で)制御する機構だ。

Skymontでは、性能重視でプリフェッチを“常に最速”で行う仕様となっていた。これに対して、Darkmontでは負荷の状況に応じて「そんなに頑張んなくてもいいでしょ?」という場面ではプリフェッチを抑制する制御を入れるようになった。

これも、消費電力を抑えるための取り組みの一環だと理解すればいい。

Nanocode Performance:特定の複雑な命令の処理を高速化

3つ目の「Nanocode Performance」を解説するには、「Nanocode(ナノコード)」の説明を先にしなければならない。

x86アーキテクチャは、CISC(復号命令セットコンピュータ)を採用している。CISC命令は可変長バイナリとなるため、最近のx86 CPUはCISC命令を機能単位の小さな命令(マイクロ命令:μOP)に分解した上で実行しており、この分解工程を「デコード」という。ここまでは知っている人も多いだろう。

デコード処理で生成されるマイクロ命令は、「隣接関係」や「メモリ内容に対する“直”演算命令」によって生成結果が変わる場合がある。そのため、場合によっては「複数からなるx86命令列」を「1つの定番の長いx86命令(マクロ命令)」に置き換えてから、それをマイクロ命令に置き換えることもある。これは「マクロ融合」と呼ばれるデコード方式だ。

少し脱線しそうになったが、x86命令デコーダーは意外と負荷の高い処理系である。そこで、パフォーマンス向上策の1つとして、特定の複雑なx86命令は生真面目にデコード処理を行わずに、「即席テンプレートからなる、カンニングペーパー的な超低遅延デコード」を行うようになった。これを「Nanocode」と呼ぶ。

Nanocodeを使った超低遅延デコードは、Skymontで初めて実装された。Darkmontにおける「Nanocode Performance」は、簡単にいうとNanocodeを利用できる命令の範囲が広がったと考えればいい。

Intelによると、この恩恵で「x86デコーダーの遅延が減って、“生真面目モード”のデコーダー処理の並列性も改善する」とのことだ。

Memory Disambiguation

「Memory Disambiguation」は、PコアであるCougar Coveの項目で解説した通りだ。

Skymontでも本機能は実装されていたが、Darkmontでも「依存予測の精度向上」「予測失敗時の回復速度向上」の2点を改善しているとのことだ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Intelの「Core Ultraプロセッサ(シリーズ3)」は2025年末に一部出荷 2026年1月にはラインアップを拡充

Intelの「Core Ultraプロセッサ(シリーズ3)」は2025年末に一部出荷 2026年1月にはラインアップを拡充

Intelが、「Panther Lake」という開発コード名で開発を進めていたCPUを新しいCore Ultraプロセッサとして発売することになった。2025年内に大量生産を開始し、同年末に一部製品の出荷を開始する見通しだ。2026年1月には、より広範な製品を集荷するという。 Intelの新型CPU「Core Ultraプロセッサ(シリーズ3)」は何が変わった? Lunar Lakeからの進化をチェック!

Intelの新型CPU「Core Ultraプロセッサ(シリーズ3)」は何が変わった? Lunar Lakeからの進化をチェック!

Intelが2025年末に出荷を開始する予定のPanther Lakeこと「Core Ultraプロセッサ(シリーズ3)」。その技術的特徴を数回に分けて解説する。今回は、全体的な概要を紹介する。 Intelが次世代CPU「Panther Lake」を“チラ見せ” 製品は2026年初頭に発売予定

Intelが次世代CPU「Panther Lake」を“チラ見せ” 製品は2026年初頭に発売予定

Intelが「Core Ultraプロセッサ(シリーズ2)」の次に投入する予定のCPU「Panter Lake」のデモンストレーションを行った。量産は2025年後半から始まる予定で、搭載製品は2025年初頭に発売される見通しだ。 Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが、VLSIシンポジウム2024に合わせて「Intel 3」の詳細を発表した。「Intel 4」の細かい部分を改良したプロセスだが、それが最大18%のパフォーマンス改善につながっているという。 「Core Ultraプロセッサ(シリーズ2)」は驚きの内蔵GPU性能に メモリ帯域が当初発表から“倍増”

「Core Ultraプロセッサ(シリーズ2)」は驚きの内蔵GPU性能に メモリ帯域が当初発表から“倍増”

IntelがLuna Lakeこと「Core Ultra 200Vプロセッサ」を発表した。Core Ultraプロセッサ(シリーズ2)のモバイル向けモデルという位置付けだが、どのような特徴があるのだろうか。ドイツ・ベルリンで開催された発表会で得られた情報をもとにまとめた。