乽Core Ultra僾儘僙僢僒乮僔儕乕僘2乯乿偼嬃偒偺撪憼GPU惈擻偵丂儊儌儕懷堟偑摉弶敪昞偐傜乬攞憹乭丗IFA 2024乮1/4 儁乕僕乯

Intel偑Luna Lake偙偲乽Core Ultra 200V僾儘僙僢僒乿傪敪昞偟偨丅Core Ultra僾儘僙僢僒乮僔儕乕僘2乯偺儌僶僀儖岦偗儌僨儖偲偄偆埵抲晅偗偩偑丄偳偺傛偆側摿挜偑偁傞偺偩傠偆偐丅僪僀僣丒儀儖儕儞偱奐嵜偝傟偨敪昞夛偱摼傜傟偨忣曬傪傕偲偵傑偲傔偨丅

丂婛曬偺捠傝Intel偼9寧3擔乮拞墰儓乕儘僢僷帪娫乯丄僪僀僣丒儀儖儕儞偱奐嵜偝傟傞乽IFA Berlin 2024乿偺奐枊偵愭棫偭偰丄儌僶僀儖岦偗怴宆CPU乽Core Ultra 200V僾儘僙僢僒乿乮奐敪僐乕僪柤丗Lunar Lake乯傪敪昞偟偨丅

- 仺怴宆SoC乽Intel Core Ultra 200V乿僔儕乕僘敪昞両丂AMD傗Qualcomm傪忋夞傞惈擻偲僶僢僥儕乕嬱摦帪娫傪傾僺乕儖丂搵嵹PC偼9寧24擔偐傜敪攧

- 仺僀儞僥儖偑乽Core Ultra僾儘僙僢僒乮僔儕乕僘2乯乿搵嵹僲乕僩PC傪崙撪弶斺業丂偳傫側儌僨儖偑偁傞丠

丂IT乛PC嬈奅慡懱偑AI乮恖岺抦擻乯偵孹搢偟偰偄偔棳傟偺拞偱丄摨幮偼偪傚偆偳1擭慜偵乽Core Ultra僾儘僙僢僒乮僔儕乕僘1乯乿傪敪昞偟偨丅偙偺帪丄摨幮偼乽AI PC乿偲偄偆僉乕儚乕僪傪宖偘丄乽PC偼AI帪戙傊乿乽AI帪戙偺PC乮偺CPU乯偲偄偊偽Core Ultra乿偲偄偆僽儔儞僨傿儞僌傪巒傔偨丅乽傕偆1擭偐乧乧乿偲丄帪偺棳傟偺憗偝傪姶偠傞丅

丂崱夞敪昞偝傟偨Core Ultra 200V僾儘僙僢僒偼乽Core Ultra僾儘僙僢僒乮僔儕乕僘2乯乿偺堦堳偲側傞丅COMPUTEX TAIPEI 2024偵崌傢偣傞宍偱丄媄弍揑側奣梫偼6寧偵敪昞嵪傒側偺偱丄乽偊丄傑偩弌偰側偐偭偨偺丠乿偲巚偆恖傕彮側偔側偄偐傕偟傟側偄丅

丂崱夞丄Intel偼儀儖儕儞偱Core Ultra 200V僾儘僙僢僒偺乬惓幃側乭敪昞夛傪峴偭偨丅偙偺婰帠偱偼敪昞夛偺庢嵽傪捠偟偰摼偨忣曬傪尦偵丄杮僾儘僙僢僒偵偮偄偰夵傔偰儗億乕僩偟偨偄丅

慡9儌僨儖峔惉丂PC儊乕僇乕偺梫朷偱捛壛儔僀儞傾僢僾偺壜擻惈傕

丂Core Ultra 200V僾儘僙僢僒偼丄慡儌僨儖偑P僐傾4婎亄E僐傾4婎乮寁8僐傾乯峔惉偲側偭偰偄傞丅嵟戝僋儘僢僋傗搵嵹偡傞儊儌儕梕検乮偛偔堦晹偺儌僨儖偼婎杮徚旓揹椡乯偺堘偄偐傜丄尰帪揰偱偼埲壓偺9儌僨儖偑梡堄偝傟偰偄傞丅

丂Intel偵傛傞偲丄偙偺儔僀儞傾僢僾偼偁偔傑偱傕9寧3擔尰嵼偺傕偺偩偲偄偆丅敪昞夛屻偺幙媈墳摎偱偼乽PC儊乕僇乕偺梫朷師戞偱偼丄彨棃揑側儔僀儞傾僢僾偺奼廩傕偁傝摼傞乿偲偄偆巪偺愢柧偑偁偭偨丅嬶懱揑偵偼乽婎杮徚旓揹椡乮PBP乯傪17W埲壓偲偟偨儌僨儖乿乮仸1乯傗乽搵嵹儊儌儕傪64GB偵憹嫮偟偨儌僨儖乿乮仸2乯偑憐掕偝傟偰偄傞偑丄偁偔傑偱傕乬壜擻惈乭掱搙偺榖偲偺偙偲偩丅

乮仸1乯Core Ultra 200V僾儘僙僢僒偺PBP偼婎杮17W乛嵟彫8W偵愝掕偝傟偰偄傞乮Core Ultra 9 288V偺傒婎杮30W乛嵟彫17W乯

P僐傾偺儅儖僠僗儗僢僪張棟傪攑巭仺儚僢僷夵慞

丂CPU僐傾偼張棟惈擻廳帇偺乽僷僼僅乕儅儞僗僐傾乮P僐傾乯乿偲丄揹椡岠棪廳帇偺乽崅岠棪僐傾乮E僐傾乯乿傪暪嵹偡傞峔惉偱曄傢傝側偄丅

丂P僐傾偼乽Lion Cove乿乮奐敪僐乕僪柤乯傪4婎搵嵹偟偰偄傞丅1婎偺暔棟僐傾偱2偮偺僗儗僢僪傪張棟偡傞乽SMT乮摨帪儅儖僠僗儗僢僨傿儞僌乛僴僀僷乕僗儗僢僨傿儞僌乯乿偵旕懳墳偱偁傞偙偲偑丄Lion Cove偺儂僢僩僩僺僢僋偩丅

丂偦偟偰E僐傾偼乽Skymont乿乮奐敪僐乕僪柤乯傪4婎搵嵹偡傞丅E僐傾偼SMT旕懳墳偩偭偨偺偱丄偙偺柺偱偺巇條揑側曄壔偼側偄丅

丂Lion Cove偲Skymont偺傾乕僉僥僋僠儍柺偺徻嵶側夝愢偼愘挊偱愢柧嵪傒側偺偱徣偔偑丄偞偭偔傝尵偆偲乽P僐傾傪SMT懳墳偝偣傞傛傝傕丄旕懳墳偲偡傞偙偲偱晜偔僩儔儞僕僗僞傗徚旓揹椡偺乬梊嶼乭傪妶梡偟偰E僐傾傪憹傗偟偨曽偑徚旓揹椡摉偨傝偺僷僼僅乕儅儞僗乮儚僢僷乯偑偄偄傫偠傖側偄丠乿偲偄偆愝寁曽恓傪嵦偭偰偄傞丅

丂偦傕偦傕SMT偼丄1婎偺僐傾偱僔儞僌儖僗儗僢僪傪幚峴偟偨嵺偵梋忚偲側傞墘嶼婍傪巊傢偣傞偨傔偺婡擻偩丅暔棟僐傾偑2僐傾偵乬暘恎乭偡傞栿偱偼側偄丅尦乆偺僔儞僌儖僗儗僢僪惈擻偺崅偄Intel偺CPU傾乕僉僥僋僠儍偱偼丄IPC乮僋儘僢僋摉偨傝偺張棟柦椷悢乯偺岦忋傪撍偒媗傔偰偄偔偵偮傟偰乽SMT偺偆傑傒乿偑惗偐偟偯傜偔側偭偨偲偄偆偙偲側偺偩傠偆丅

P僐傾偺愝寁曽恓傪徻偟偔恾帵偟偨僗儔僀僪丅僞僀僩儖偼僘僶儕乽PPA乮惈擻岠棪乛揹椡岠棪乛柺愊岠棪乯傪傛傝椙偔偡傞偨傔偺SMT偺攑巭乿偲偄偆偙偲偱丄SMT婡峔傪攑巭偡傞偙偲偱摼傜傟傞儊儕僢僩傪夝愢偟偰偄傞

丂壓偵宖嵹偡傞恾偼丄Intel偑帺幮偱挷傋偨乽Lunar Lake懳Meteor Lake乿偺僷僼僅乕儅儞僗斾妑偩丅

丂僷僢働乕僕偺徚旓揹椡傪乽17W乿偵偦傠偊偰斾妑偡傞偲丄Lunar Lake偼丄Meteor Lake乮僔儕乕僘1乯偺16僐傾22僗儗僢僪儌僨儖乮P僐傾6婎12僗儗僢僪亄E僐傾8婎8僗儗僢僪亄LP E僐傾2婎2僗儗僢僪乯傛傝傕惈擻偑椙偄偺偩偲偄偆丅偙傟偑乽23W埲忋乿偲側傞偲丄偝偡偑偵Meteor Lake偑媡揮偡傞偺偩偑丄嵎偼傢偢偐6亾偟偐側偄丅

丂壖掕偺榖偩偑丄Lunar Lake偵傛傝懡偔偺CPU僐傾乮12婎偔傜偄乯傪搵嵹偡傞峔惉偑偁偭偨偲偟偨傜丄23W埲忋偵偍偗傞媡揮傪嫋偝側偄偩傠偆丅

徚旓揹椡傪偦傠偊偰Lunar Lake偲Meteor Lake偺惈擻傪斾妑偟偨僌儔僼丅17W傑偱偼Lunar Lake偺曽偑桪傟偨僷僼僅乕儅儞僗傪妋曐偱偒偰偄傞丅23W偵側傞偲Meteor Lake偑媡揮偡傞偺偩偑丄偦偺嵎偼6亾偟偐側偔乽儚僢僷乿柺偱岠棪偑椙偔側偄偙偲偑暘偐傞

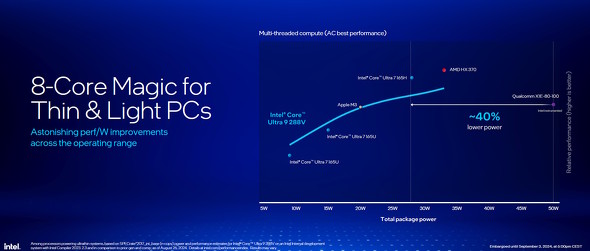

丂師偺僌儔僼偼丄崱夞敪昞偝傟偨拞偱嵟忋埵偲側傞乽Core Ultra 9 288V乿偺惈擻傪丄摨偠30W僋儔僗偺嫞崌CPU偲斾傋偨僋儔僼偩丅嬶懱揑偵偼丄AMD偺乽Ryzen AI 9 HX 370乿偲丄Qualcomm偺乽Snapdragon X Elite X1E-80-100乿偲斾傋偰偄傞丅

丂8僐傾8僗儗僢僪偺CPU偱偁傝側偑傜丄Core Ultra 9 288V偼徚旓揹椡懳惈擻偵偍偄偰12僐傾24僗儗僢僪偺Ryzen AI 9 HX 370偵乬擏敆乭偡傞乗乗Intel偼偙傟偱傕偐偲丄偙偺揰傪嫮挷偟偰偄偨丅偦偟偰Snapdragon X Elite X1E-80-100偵偮偄偰偼丄惈擻偺妱偵徚旓揹椡偑戝偒偡偓傞椺偲偟偰弌偟偨偺偩傠偆丅

丂偦偺堄恾偑偁傞偺偐偳偆偐偼晄柧偩偑丄Intel偼崱夞偺僾儗僛儞僥乕僔儑儞偱Snapdragon X Elite X1E-80-100傪丄偄傢偽乽偍徫偄扴摉乿偲偟偰埖偭偰偄傞傛偆偵傕尒偊偨丅

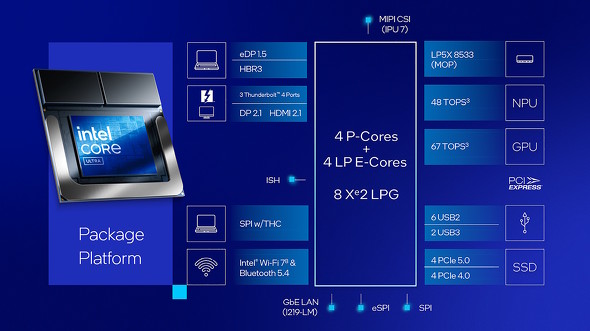

Core Ultra 200V僔儕乕僘偺僽儘僢僋僟僀儎僌儔儉丅崱夞偼儊儌儕僠僢僾傗Wi-Fi乛Bluetooth捠怣婡擻丄Thunderbolt 4僐儞僩儘乕儔乕傕摑崌偟偰偄傞偨傔丄Intel偼摨僔儕乕僘傪乽CPU乿偱偼側偔乽SoC乿偲屇傇偙偲偑懡偄

儊儌儕僶僗偼乽64bit乿偐傜乽128bit乿偵掶惓

丂Core Ultra 200V僾儘僙僢僒偼丄僠僢僾忋偵LPDDR5X-8533婯奿偺儊儌儕儌僕儏乕儖傪搵嵹偟偰偄傞丅丄6寧偵峴傢傟偨婡擻奣梫偺愢柧偱偼丄偦偺僀儞僞僼僃乕僗偑乽64bit乿偱偁傞偲偝傟偨丅

丂崱夞偺敪昞夛偱偼丄杮審偵偮偄偰嵞搙婰幰偐傜幙栤偑偁偭偨丅偡傞偲儘僶乕僩丒僴儘僢僋巵乮僋儔僀傾儞僩僐儞僺儏乕僥傿儞僌僌儖乕僾 AI乛僥僋僯僇儖儅乕働僥傿儞僌扴摉僶僀僗僾儗僕僨儞僩寭僕僃僱儔儖儅僱乕僕儍乕乯偑丄乽偙偺審偵偮偄偰岆夝乮儈僗僐儈儏僯働乕僔儑儞乯偑偁偭偨乿偲偟偨忋偱丄幚偼乽64bit亊2乮僨儏傾儖僠儍僱儖乯偺128bit僶僗愙懕偩偭偨乿偲掶惓傪峴偭偨丅偮傑傝丄儊儌儕僶僗偼Core Ultra乮僔儕乕僘1乯偲摨摍偲偄偆偙偲偵側傞丅

丂LPDDR5X-8533婯奿偺儊儌儕偑128bit偱愙懕偝傟傞偲偄偆偙偲偼丄棟榑忋偺嵟戝傾僋僙僗懍搙偼枅昩栺136GB偲側傞丅Core Ultra乮僔儕乕僘1乯偑枅昩栺120GB偩偭偨偙偲傪摜傑偊傞偲丄傢偢偐偩偑儊儌儕傾僋僙僗偺僗僺乕僪偑夵慞偝傟傞丅

丂偙偙傑偱偺懷堟偑偁傟偽丄偦傟側傝偵崅偄僎乕儈儞僌惈擻傗丄AI張棟惈擻丄儊僨傿傾張棟惈擻偑婜懸偱偒偦偆偩丅

Copyright © ITmedia, Inc. All Rights Reserved.

娭楢婰帠

僀儞僥儖偑乽Core Ultra僾儘僙僢僒乮僔儕乕僘2乯乿搵嵹僲乕僩PC傪崙撪弶斺業丂偳傫側儌僨儖偑偁傞丠

僀儞僥儖偑乽Core Ultra僾儘僙僢僒乮僔儕乕僘2乯乿搵嵹僲乕僩PC傪崙撪弶斺業丂偳傫側儌僨儖偑偁傞丠

擔杮帪娫偺怺栭丄Core Ultra僾儘僙僢僒乮僔儕乕僘2乯偑敪昞偝傟偨丅偦傟傪庴偗偰丄僀儞僥儖偑僀儀儞僩偺婎挷島墘偵偍偄偰摨僾儘僙僢僒傪崙撪偱弶傔偰偍斺業栚偟偨丅暪偣偰丄揥帵夛応偱偼堦晹儊乕僇乕偺搵嵹PC偺揥帵傕峴傢傟偨丅 怴宆SoC乽Intel Core Ultra 200V乿僔儕乕僘敪昞両丂AMD傗Qualcomm傪忋夞傞惈擻偲僶僢僥儕乕嬱摦帪娫傪傾僺乕儖丂搵嵹PC偼9寧24擔偐傜敪攧

怴宆SoC乽Intel Core Ultra 200V乿僔儕乕僘敪昞両丂AMD傗Qualcomm傪忋夞傞惈擻偲僶僢僥儕乕嬱摦帪娫傪傾僺乕儖丂搵嵹PC偼9寧24擔偐傜敪攧

Intel偑Lunar Lake乮奐敪僐乕僪柤乯偲屇偽傟偰偄偨儌僶僀儖岦偗怴CPU乽Intel Core Ultra 200V乿僔儕乕僘傪惓幃偵敪昞偟偨丅 僀儞僥儖偑乽Lunar Lake乿偺僠僢僾幚暔傪斺業丂幚偼尰峴乽Core Ultra乿偺捈愙屻宲偱偼側偄丂偦偺棟桼偼丠

僀儞僥儖偑乽Lunar Lake乿偺僠僢僾幚暔傪斺業丂幚偼尰峴乽Core Ultra乿偺捈愙屻宲偱偼側偄丂偦偺棟桼偼丠

僀儞僥儖偑奐嵜偟偨曬摴娭學幰岦偗僙儈僫乕偵偍偄偰丄2024擭廐埲崀偵搊応偡傞梊掕偺乽Lunar Lake乿偺乬幚暔乭偑岞奐偝傟偨丅Lunar Lake偼儌僶僀儖僲乕僩PC岦偗偺SoC偱丄摨幮偲偟偰偼弶傔偰儊儌儕僠僢僾傪儌僕儏乕儖幚憰偟偰偄傞偙偲偑摿挜偩丅 師悽戙CPU乽Lunar Lake乿偱Intel偑栚巜偡乬AI PC乭偲偼丠丂嬃偔傋偒恑壔揰偲尒偊傞庛揰丄偦偺崕暈朄

師悽戙CPU乽Lunar Lake乿偱Intel偑栚巜偡乬AI PC乭偲偼丠丂嬃偔傋偒恑壔揰偲尒偊傞庛揰丄偦偺崕暈朄

COMPUTEX TAIPEI 2024偵愭棫偭偰丄Intel偑崱屻敪攧偝傟傞梊掕偺CPU偵娭偡傞媄弍愢柧夛傪奐嵜偟偨丅偙偺婰帠偱偼丄2024擭戞4巐敿婜偵搊応偡傞梊掕偺儌僶僀儖岦偗CPU乽Lunar Lake乿乮奐敪僐乕僪柤乯偺媄弍揑奣梫傪徯夘偡傞丅 Intel偺師悽戙CPU偼乽Core Ultra僾儘僙僢僒乿偲偟偰12寧14擔乮暷崙懢暯梞帪娫乯偵惓幃敪昞

Intel偺師悽戙CPU偼乽Core Ultra僾儘僙僢僒乿偲偟偰12寧14擔乮暷崙懢暯梞帪娫乯偵惓幃敪昞

Intel偑乽Meteor Lake乿偲偟偰奐敪傪恑傔偰偒偨師悽戙CPU傪乽Core Ultra僾儘僙僢僒乿偲偟偰斕攧偡傞偙偲傪惓幃偵敪昞偟偨丅徻嵶側僗儁僢僋丄儔僀儞傾僢僾側偳偼12寧14擔乮暷崙懢暯梞帪娫乯偵柧傜偐偲側傞丅