ニュース

Intel、Broadwell世代の「Core M」概要を公開:14ナノプロセスルールで性能改善(2/2 ページ)

最初の搭載モデルは2014年のクリスマス商戦に登場する予定だ。

第2世代トライゲートの導入でパッケージサイズをさらに削減

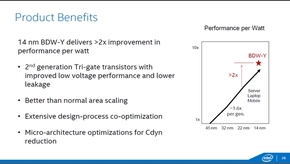

製造技術ではプロセスルールの微細化と第2世代のトライゲートトランジスタの導入でパッケージの底面積がHaswell世代の半分に、高さも30%削減となったほか、電力効率が改善した。また、Turbo Boost Technologyも拡張して消費電力と熱管理の最適化が進んだ。このことで、ワット当たりの処理性能は2倍に向上し、アイドル状態の消費電力は60%も向上したという。

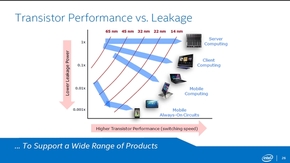

22ナノメートルプロセスルールから14ナノメートルプロセスルールへの移行でワット当たりの性能は2倍に向上する(写真=左)。プロセスルールの縮小とリーク電流の関係。軽量薄型のノートPCに搭載するCPUで、リーク電流の削減が大きく改善する(写真=右)

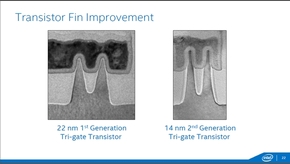

22ナノメートルプロセスルールから14ナノメートルプロセスルールへの移行でワット当たりの性能は2倍に向上する(写真=左)。プロセスルールの縮小とリーク電流の関係。軽量薄型のノートPCに搭載するCPUで、リーク電流の削減が大きく改善する(写真=右)22ナノメートルプロセスルールから14ナノメートルプロセスルールへの移行でパッケージサイズが削減した理由としては、トランジスタのフィン間隔(60ナノメートルから42ナノメートル)やゲート間隔(90ナノメートルから70ナノメートル)、インターコネクト間隔(80ナノメートルから52ナノメートル)と縮小したことが貢献したとIntelは説明している。

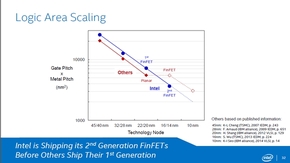

トライゲートトランジスタのフィン間隔を第1世代と第2世代で比較する(写真=左)。プロセスルールの縮小に伴うパッケージサイズの推移。競合は14ナノメートルプロセスルールを導入してもパッケージサイズを縮小できないとインテルは主張する(写真=右)

トライゲートトランジスタのフィン間隔を第1世代と第2世代で比較する(写真=左)。プロセスルールの縮小に伴うパッケージサイズの推移。競合は14ナノメートルプロセスルールを導入してもパッケージサイズを縮小できないとインテルは主張する(写真=右)Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

大解説! 次期CPUに対応する新世代“冷却”事情

大解説! 次期CPUに対応する新世代“冷却”事情

“Devil's Canyon”“Broadwell”では、従来の冷却機構が対応できないという。次期CPUに向けたクーラーユニット、PCケース、電源ユニットの動きを解説する。 大復習! Haswell RefreshからDevil's Canyon、Intel 9シリーズチップセットを整理する

大復習! Haswell RefreshからDevil's Canyon、Intel 9シリーズチップセットを整理する

“新しい”第4世代Coreプロセッサー・ファミリーとチップセットは、これまでと何が違うのか? 期待の“アンロック”なCPUとともにおさらいしておこう