Intelが「第4世代Xeonスケーラブルプロセッサ」を正式発表 後から機能を拡張できる「Intel On Demand」対応モデルも

Intelが、データセンター(サーバ)/HPC向けCPU「Xeonスケーラブルプロセッサ」の第4世代製品を正式に発表した。先行リリースされたHBM2付きの「Xeon CPU Max」と合わせて、一部モデルを除き後から機能を追加できる「Intel On Demand」にも対応する。

Intelは1月10日(米国太平洋時間)、データセンター(サーバ)/HPC(ハイパフォーマンスコンピューティング)向けCPU「第4世代Xeonスケーラブルプロセッサ」(開発コード名:Sapphire Rapids)を正式に発表した。先に発表済みの「Intel Xeon CPU Maxシリーズ」と合わせて、1月から順次量産モデルの出荷が開始される予定だ。

第4世代Xeonスケーラブルプロセッサの概要

第4世代Xeonスケーラブルプロセッサは、先述の通り「Sapphire Rapids」という開発コード名の下で開発が進められてきた。Intel Xeon CPU MaxシリーズがHBM2(広帯域メモリ)を統合したモデルであるのに対し、第4世代XeonスケーラブルプロセッサはHBM2を統合しない(≒外部メモリが必須の)モデルという位置付けとなる。

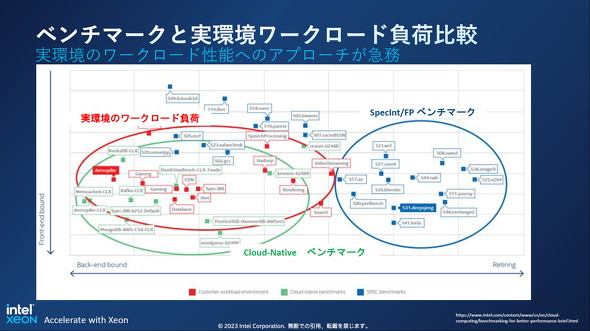

Sapphire Rapidsは「実環境のワークロード(演算処理)性能」の向上の最優先して作られたアーキテクチャだという。

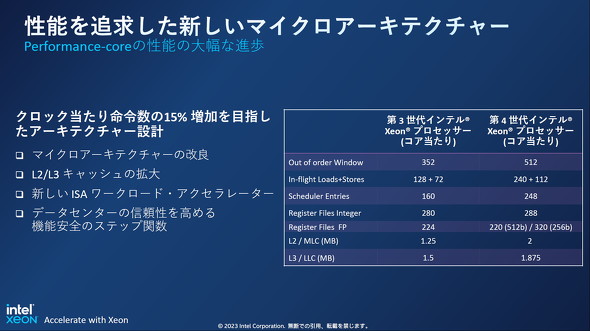

CPUコアは、第12世代/第13世代Coreプロセッサと同じパフォーマンスコア(Pコア、開発コード名:Golden Cove)を採用した。これにより、IPC(クロック当たりの処理命令数)は「第3世代Xeonスケーラブルプロセッサ(開発コード名:Ice Lake)」比で最大15%の向上を果たしたという。

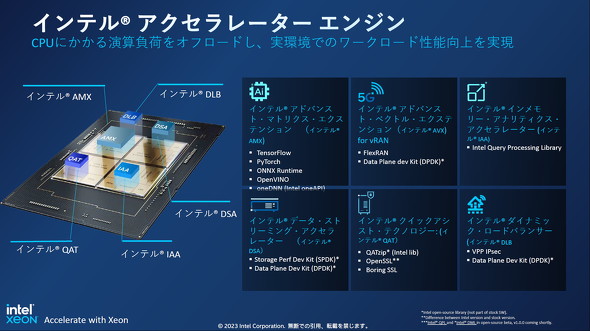

加えて、CPUコアの処理をオフロードするためのアクセラレーター(演算エンジン)を別途搭載できる構造としている。

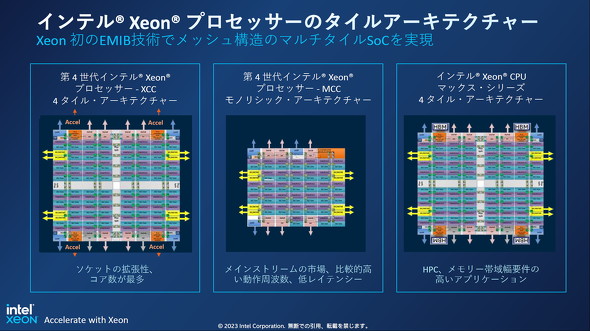

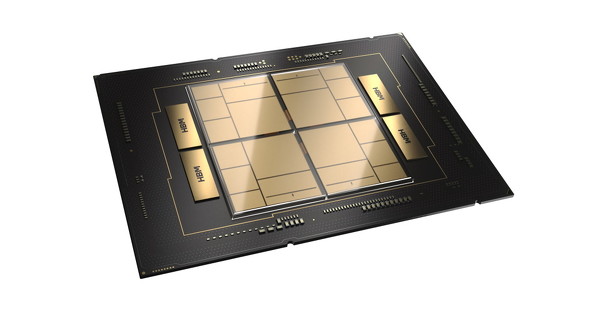

Sapphire Rapidsの最大の特徴は、1つのプロセッサに搭載するチップの枚数や種類を柔軟に変えられる「タイル設計(チップレット技術)」を採用していることにある。このことを生かして、Sapphire Rapidsでは大きく以下の3種類のタイル構造を採用している。

- MCC(Medium Core Count)パッケージ:メインストリームモデル

- タイルは1枚のみ(モノシリック構造)

- CPUコアは最大32基(64スレッド)

- マルチプロセッサは最大2基構成に対応(※1)

- CPUコアの動作クロックと低レイテンシーを重視するユーザー向け

- XCC(Extreme Core Count):ハイエンドモデル

- タイルは4枚

- CPUコアは最大60基(120スレッド)

- マルチプロセッサは最大8基構成に対応(※2)

- とにかく「CPUコアの数」を重視したいユーザー向け

- Xeon CPU Maxシリーズ

- XCCにHBM2を追加搭載(XCC構成モデルのバリエーション)

- HBM2の容量は最大64GB(今回登場したモデルは全て64GB構成)

- CPUコアは最大56基(112スレッド)

- マルチプロセッサは最大2基対応(全モデル共通)

- DDR5メモリでも「アクセス速度が足りない」という用途向け

(※1)マルチプロセッサ構成に対応しないモデルもあり

(※2)モデルによって「マルチプロセッサ非対応」「最大2基」「最大4基」「最大8基」と異なる

CPUコアの処理をオフロードするためのアクセラレーター類は、以下の5種類を内蔵している。ただし、モデルによって搭載(有効化)されている基数が異なる。

- Advanced Matrix Extension(Intel AMX)

- タイル化した二次元行列の演算を専門に行うプロセッサ

- 機械学習ベースのAI(人工知能)における推論/学習処理を高速化できる

- Dynamic Load Balancer(Intel DLB)

- ネットワークのパケット処理をコア/スレッド単位で分散処理できる

- Data Streaming Accelerator(Intel DSA)

- システム内のデータ転送(キャッシュ→メインメモリ、メインメモリ同士、メインメモリ→I/Oなど)を高速化する

- In-Memory Analytics Accelerator(Intel IAA)

- データベース処理における「スキャン」「フィルター」「圧縮」「伸長」を行う

- データベースのスループット(実効速度)を向上できる

- Quick Assist Technology(Intel QAT)

- 暗号化とデータ圧縮を高速化する

- 第3世代Xeonスケーラブルプロセッサではチップセットに実装していたが、CPUに統合することでパフォーマンスを向上

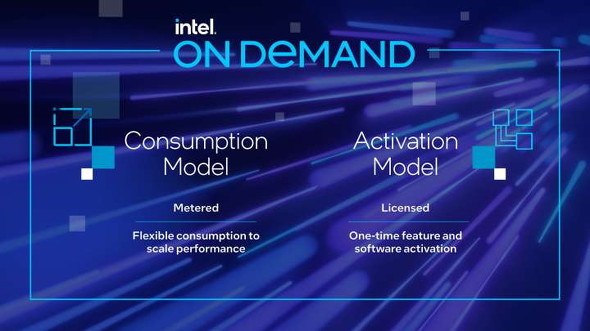

なお、モデル名末尾に「H」が付いているモデル(動画配信/分析/仮想化に最適化されたモデル)と、シリーズ全体のエントリーモデルとなる「Xeon Bronze 3408U」以外は、後からアクセラレーター類や追加機能を有料で有効化できる「Intel On Demand」というサービスに対応している。このサービスで有効化/追加できるアクセラレーターと機能は以下の通りとなる。

- DLB

- DSA(※3)

- QAT

- IAA

- DSA(※3)

- Security Guard Extensions(Intel SGX)

(※3)プロセッサに当該アクセラレーターが備わっている場合のみ対応

Intel On Demandのサービスは、Intelまたは指定プロバイダーにリクエストすることで恒久的に有効化できる「アクティベーションモデル」と、SaaS形式で一時的に機能を有効化/追加できる「消費モデル」の2種類が用意されている。利用できるサービスはプロバイダーによって異なる。

第4世代Xeonスケーラブルプロセッサには、CPUコア外にハードウェアベースのアクセラレーターを最大5種類搭載している。有効化されているアクセラレーターの種類と基数はモデルによって異なるが、DSAは全モデル共に少なくとも1基搭載している

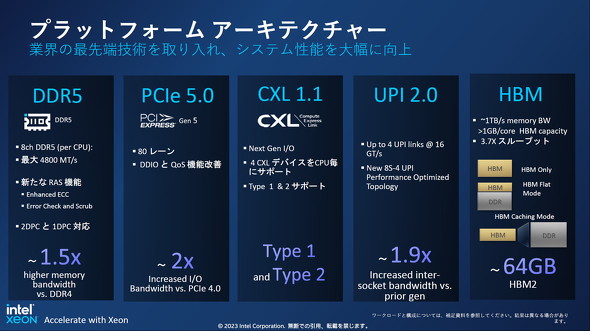

メインメモリはDDR5規格だが、最大速度はモデルによって異なる。CPU直結のPCI Express 5.0バスは80レーンを備え、CXL(Compute Express Link) 1.1準拠機器もCPU1台当たり4台接続できる(※4)。

(※4)CXL 1.1はローカルメモリを持たないアクセラレーター向けの「Type 1」と汎用(はんよう)アクセラレーター向けの「Type 2」に対応する

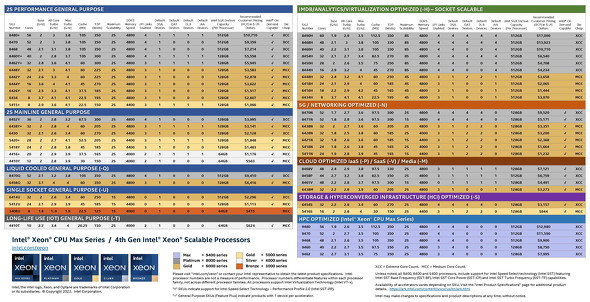

ラインアップ

1月11日(米国太平洋時間)現在、第4世代Xeonスケーラブルプロセッサのラインアップは以下の通りとなる。

- 汎用モデル:24種類

- 2モデルは液冷対応

- 3モデルはマルチプロセッサ構成非対応

- 1モデルは長寿命/IoT用途向け

- 動画配信/分析/仮想化に最適化されたモデル:10種類

- 5G/ネットワーク機器向けモデル:7種類

- うち3モデルはマルチプロセッサ構成非対応

- HCI/ストレージ向けモデル:2種類

- Xeon CPU Maxシリーズ:5種類

今後のXeonスケーラブルプロセッサの展開

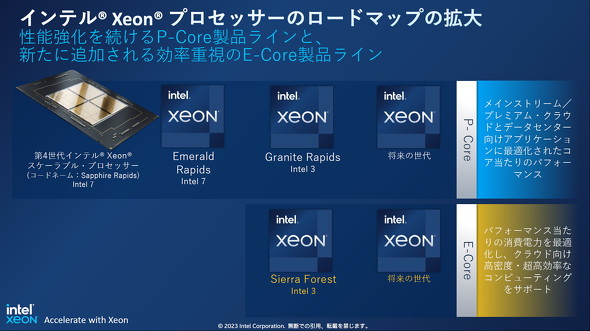

今回(第4世代)のXeonスケーラブルプロセッサは、Pコアを備えるモデルのみ用意されている。既報だが、今後2世代のXeonスケーラブルプロセッサは以下のスケジュールで“進化”していく予定だ(名称はいずれも開発コード名)。

- 2023年内出荷開始予定:Emerald Rapids

- 今回登場したSapphire Rapidsの改良版

- 2024年内出荷開始予定:Granite Rapids/Sierra Forest

- Granite RapidsはEmerald Rapidsの後継でPコアのみの構成

- Sierra Forestは低消費電力重視で高効率コア(Eコア)のみの構成

- 両者共に「Intel 3(7nmプロセス)」で製造

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ついに! ようやく? 「Intel Maxシリーズ」2023年1月から出荷 HBM付き「Xeon Max」と高密度実装GPU「Intel GPU Max」

ついに! ようやく? 「Intel Maxシリーズ」2023年1月から出荷 HBM付き「Xeon Max」と高密度実装GPU「Intel GPU Max」

Intelが、HPC(ハイパフォーマンスコンピューティング)と機械学習ベースのAI(人工知能)用のCPU/GPUの統一ブランドとして「Intel Max」を立ち上げる。その第1弾製品はSappire Rapidsと呼ばれていたCPU「Xeon Maxプロセッサ」と、Ponte Vecchioと呼ばれていた「Intel Data Center GPU Max」である。 IntelがPC向けCPU/GPUのロードマップを更新 「Raptor Lake」は2022年後半に

IntelがPC向けCPU/GPUのロードマップを更新 「Raptor Lake」は2022年後半に

Intelが投資家向けのイベントでCPU/GPUの最新ロードマップを公表した。第12世代Coreプロセッサの後継となる「Raptor Lake(ラプターレイク)」は2022年後半に登場するという。 Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

スーパーコンピューターの世界的なイベント「ISC 2021」に合わせて、IntelがHPC(ハイパフォーマンスコンピューティング)に関する取り組みを発表した。その中で、次世代のXeonスケーラブルプロセッサ(開発コード名:Sapphire Rapids)にHBM(広帯域メモリ)を内蔵するバージョンが用意されることが明らかとなった。 通信インフラでの利用を想定 Intelが新型「Xeon Dプロセッサ」を投入

通信インフラでの利用を想定 Intelが新型「Xeon Dプロセッサ」を投入

エッジコンピューティングを含む通信インフラ機器での利用を想定した「Xeon Dプロセッサ」がモデルチェンジした。CPU部分はIce Lakeアーキテクチャベースとなり、CPU直結のPCI Express 4.0バスも用意される。 Intelが「第3世代Xeonスケーラブルプロセッサ(Ice Lake)」を発表 最大40コアで処理能力を向上

Intelが「第3世代Xeonスケーラブルプロセッサ(Ice Lake)」を発表 最大40コアで処理能力を向上

Intelが、Ice Lakeアーキテクチャに基づく第3世代Xeonスケーラブルプロセッサを発表した。クロック当たりの処理性能を向上し、機械学習ベースのAI処理も高速化している。なお、既存のCooper Lakeアーキテクチャの製品は継続販売(併売)される。