Intel 18AプロセスのEコアオンリーCPU「Xeon 6+(Clear Water Forest)」はどんなCPU? 詳細を解説(3/4 ページ)

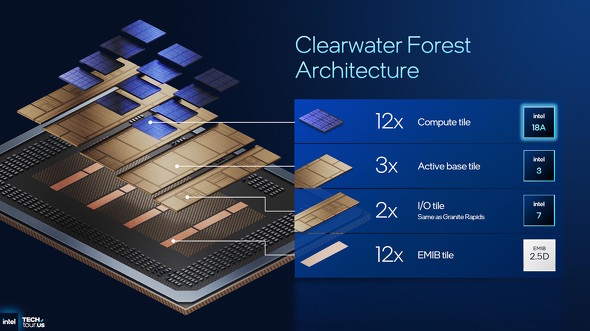

Intelが2026年前半にリリースする予定のサーバ/データセンター向けCPU「Xeon 6+プロセッサ」(開発コード名:Clearwater Forest)は、Eコアオンリーの製品としては一気に2世代相当の進化を遂げている。その詳細を見ていこう。

ベースタイルとI/Oタイルの構造は?

Clearwater Forestは、Intelの最新パッケージング技術「EMIB 2.5D」「Foveros Direct 3D」を採用しており、Computeタイルを「ベースタイル」を介して他のタイルと相互接続(Interconnect)している。相互接続の詳細については次項に譲って、ここでは相互接続に使うベースタイルと、各種入出力を担う「I/Oタイル」について解説していく。

「Intel 3」で作られたベースタイル

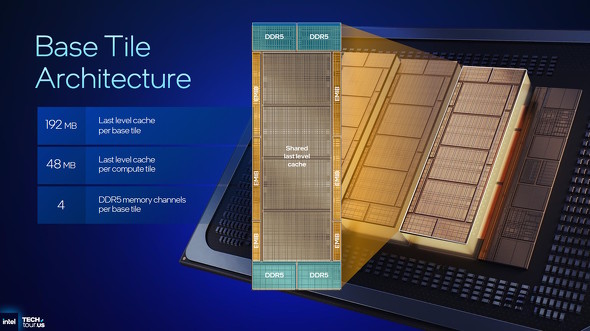

ベースタイルは、他のダイを結び付ける、いわば“中核”を担うタイルだ。3nm相当の「Intel 3」プロセスで作られており、タイル同士をつなぐための配線などを備えている。

先代のGranite Rapidsでは、メモリインタフェースをI/Oダイに搭載していたが、今回のClearwater Forestではベースタイル側に移設された。また、L3キャッシュもベースタイル上にある。

さらに、配線以外のアクティブロジックについてもベースタイルが面倒を見る形を取るようになったので、Clearwater Forestのベースタイルは「アクティブベースタイル」とも呼ばれる。下図はそのレイアウトイメージで、最大規模だと3基用意される。

ベースタイル同士の接合は、EMIB 2.5Dで行われる。ベースタイルには1基当たり192MBのL3キャッシュを搭載している。最大576MBのL3キャッシュは、「192MB×ベースタイル3基」という構成の場合の値となる。

ベースタイルのメモリコントローラーは4チャンネル構成となっている。最大構成の場合、メモリコントローラーは4チャンネル×3=12チャンネルを備えることになる。

ここでもう一度、ベースタイルの図解を見ると、L3キャッシュが4つのセグメント(区画)に分けた感じで描かれているのが見て取れる。これは1セグメント当たり48MBのL3キャッシュを備えていることを意味する。

Computeタイルが1基当たり最大24基のCPUコアを有していることは解説済みだが、このComputeタイルたちは、ベースタイルで縦に並んだL3キャッシュセグメントの“直上に”ぴったりと1つずつFoveros Direct 3Dで接合される。巨大なキャッシュダイをCPUダイにピンポイントで接合する技術は、AMDがRyzenシリーズに適用している「3D V-Cache」とよく似ている。

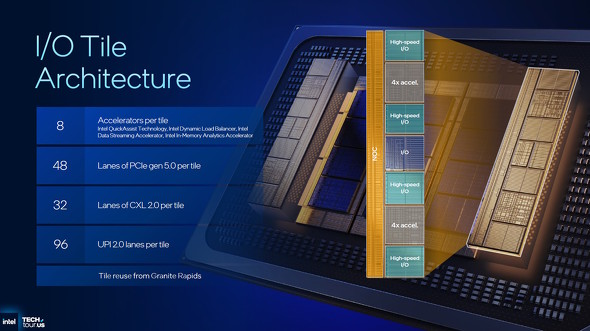

「Intel 7」で作られたI/Oタイル

PCI Expressバス、CXLバス、UPI(Ultra Path Interconnect)バスなど、各種入出力インターフェースを集約している「I/Oタイル」は、7nm相当の「Intel 7」プロセスで生産されている。

Clearwater ForestのI/Oタイルは、パッケージの両端に1基ずつ合計2基を搭載している。上の図で表されているのは、1基あたりの図解ということだ。図解の左側には「タイル1基当たりに内包される機能ブロックの数」が示されているので、パッケージ全体では2倍の数を備えていることには留意してほしい。

I/Oタイルにある8基の「アクセラレーター」は第4世代Xeonスケーラブルプロセッサ(開発コード名:Sapphire Rapids)から継続して搭載しているもので、具体的には以下のものを指す。

- Intel QAT (QuickAssist Technology)

- Intel DLB (Dynamic Load Balancer)

- Intel DSA (Data Streaming Accelerator)

- Intel IAA (In-Memory Analytics Accelerator)

それぞれのアクセラレーターの機能は、以前に第5世代製品(開発コード名:Emerald Rapids)の記事で解説しているので、気になる人は参照してほしい。

PCI Express 5.0バスは、1基当たり48レーン、CXL 2.0バスは1基当たり32レーン、UPI 2.0バスは1基当たり96レーンを備えている。

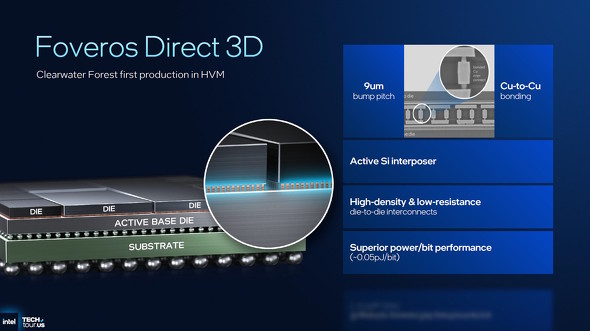

先進パッケージング技術「EMIB 2.5D」「Foveros Direct 3D」を採用

Clearwater Forestで使われているパッケージング技術は、Intelが持つ技術の“見本市”のような側面がある。EMIB 2.5DとFoveros Direct 3Dについて、それぞれ見ていこう。

EMIB 2.5D

「EMIB 2.5D」のEMIBは「Embedded Multi-die Integrated Bridge」の略となる。簡単に説明すると、平面方向に並べた複数のダイを、インターポーザー基板を介して接続するパッケージスタイルとなる。

現在、主に活用されているのは第2世代EMIBと呼ばれる、55μm〜45μmのバンプピッチだとされる。

Foveros Direct 3D

「Foveros Direct 3D」はIntelが誇る最先端パッケージ技術の1つで、切り出された単体ダイとウエハとの接合(D2W:Die to Wafer)、あるいはウエハ“全体”の相互直接接合(W2W:Wafer to Wafer)が可能だとされる。接合時は「はんだバンプ」を使わず、銅と銅を直接熱処理して原子レベルで接合する。

今回のClearwater Forestにおける接合ピッチは、第1世代の9μmで行ったという。ちなみに、第2世代では接合ピッチが3μmにまで短縮されているそうだ。

ここで1つ補足しておくと、EMIB 2.5DとFoverosを併用すると、EMIB 2.5Dはブランド的に「EMIB 3.5D」と呼ばれるようになるという“呼称名成長マジック”がある。

Intelのパッケージング技術には、今回ここで取り上げたもの以外にも、「FCBGA 2D/2D+」「Foveros 2.5D/3D」などがあるが、これらについてさらに知りたい人は過去の記事を参照してほしい。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Intelがモバイル向け「Core Ultraプロセッサ(シリーズ3)」を正式発表 搭載製品は1月27日(米国太平洋時間)から順次出荷

Intelがモバイル向け「Core Ultraプロセッサ(シリーズ3)」を正式発表 搭載製品は1月27日(米国太平洋時間)から順次出荷

Intelがモバイル向け「Core Ultraプロセッサ(シリーズ3)」を正式発表した。搭載モデルは1月27日(米国太平洋時間)から順次出荷される。【訂正】 2025年末出荷開始予定の「Core Ultraプロセッサ(シリーズ3)」のCPUコア構造を“深掘り”

2025年末出荷開始予定の「Core Ultraプロセッサ(シリーズ3)」のCPUコア構造を“深掘り”

Intelが2025年末に一部モデルを出荷する予定の「Core Ultraプロセッサ(シリーズ3)」(開発コード名:Panther Lake)だが、CPUコアを改良しているという。どう改良されているのか、解説しよう。 Sierra Forest/Granite Rapidsは「Xeon 6プロセッサ」に――IntelがXeonプロセッサをリブランド

Sierra Forest/Granite Rapidsは「Xeon 6プロセッサ」に――IntelがXeonプロセッサをリブランド

Coreプロセッサに続き、IntelがXeonプロセッサのリブランドを実施する。プロセッサ名の一部に世代数が入るようになるが、具体的なモデル名がどうなるのかには言及がない。 そのあふれる自信はどこから? Intelが半導体「受託生産」の成功を確信する理由【中編】

そのあふれる自信はどこから? Intelが半導体「受託生産」の成功を確信する理由【中編】

Intelが、半導体の受託生産事業「Intel Foundry」を本格的にスタートした。受託生産事業者(ファウンドリー)としては新参者でありながら、同社は既に自信満々のようである。それはなぜなのか、ちょっと深掘りして考察していこうと思う。 「第5世代Xeonスケーラブルプロセッサ」はどう変わったのか? その秘密を技術解説する

「第5世代Xeonスケーラブルプロセッサ」はどう変わったのか? その秘密を技術解説する

当初予告されていた通り、Intelが12月14日に「第5世代Xeon スケーラブルプロセッサ」(開発コード名:Emerald Rapids)を発表した。第4世代と同じCPUソケットを採用していることから「マイナーチェンジ」とも見られがちだが、実は変更/改良点が多岐に渡っている。2023年11月末に米国で行われた説明会の内容をもとに、その変化をチェックしていこう。