「Meteor Lake」はCPUコアが3種類!? Intelが次世代CPUの詳細を発表(前編):正式発表は12月14日(米国太平洋時間)(1/3 ページ)

Intelが、次世代CPUとして2023年末に正式発表する予定の「Meteor Lake」のアーキテクチャ面での詳細を発表した。この記事では、CPUコアを備える「Compute Tile」と、高度な機能を複数搭載する「SoC Tile」にある“謎の新要素”について詳説する。

Intelは9月19日(米国太平洋夏時間)、12月14日(同)に正式発表される予定のモバイル向け次世代CPU「Core Ultraプロセッサ」(開発コード名:Meteor Lake)のアーキテクチャの詳細を発表した。

本CPUは、同社自身が「ここ40年間で最も大きなアーキテクチャシフトを行った」と公言している。それほどに“自信たっぷり”な製品のようだ。

その自身の裏付けは、民生向けCPUの製造技術における「初採用」の技術が数多く盛り込まれたことにある。筆者は発表に先駆けて技術説明会に参加したが、その内容は非常に興味深く、とても“濃い”ものだった。

そこで今回、前後編の2回に分けてMeteor Lakeの特徴を解説することにした。この記事(前編)では、読者の皆さんが一番関心を寄せているであろうMeteor Lakeにまつわる「製造技術」と「CPUコア」を中心に解説していきたい。

Meteor Lakeを下支えする製造技術「Foveros」とは?

Meteor Lakeは、ユーザーの手元に届く製品となった際には「CPU」とか「プロセッサ」と呼ばれたりすることのなるだろうが、製品カテゴリーとしては、CPUを含む複数の機能を統合した「SoC(System on a Chip)」と呼ばれる半導体製品となる。

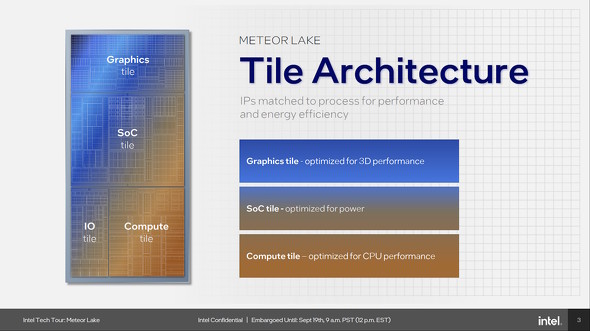

その最大の特徴は、IntelのSoCとしては初めて「タイルアーキテクチャ」を採用したことにある。タイルアーキテクチャとは、SoC(CPU)を単一のダイ(モノシリックダイ)として形成するのではなく、機能ごとに分かれた「機能ブロック」と呼ばれるダイを複数組み合わせて1つの「パッケージ」を作り、それを1つのSoCとして形成する手法だ。

機能ブロックは、小さなチップを意味する「チップレット」とも呼ばれる。そのこともあり、タイルアーキテクチャは一般的に「チップレット技術(アーキテクチャ)」と説明されることが多い。

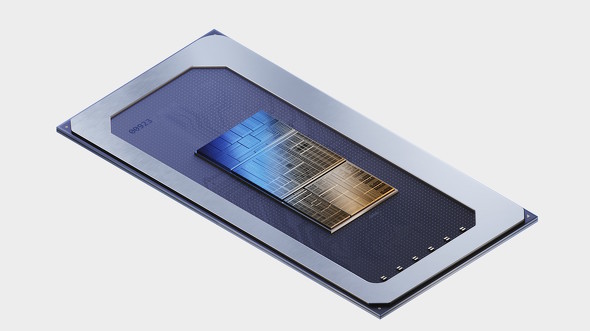

記者説明会で使われたスライドの1つ。左側にあるこまごまとしたものはMeteor Lakeのパッケージの概略図で、大きく分けると4つのタイル(チップレット)を組み合わせて作られていることが分かる(詳しくは後述)

チップレット技術によるCPU(SoC)の開発は、競合のAMDが「Zen 2アーキテクチャ」で既に実現している。Zen 2アーキテクチャといえば、2019年夏に登場したデスクトップ向けの「Ryzen 3000シリーズ」が初出なので、Intelはチップレット技術を「4年遅れ」で採用したともいえる。

しかし、Meteor Lakeにおけるタイルアーキテクチャを細かく見ていくと、IntelはAMDのチップレットよりも“先進度”の高いことに取り組んでいることが分かる。

Meteor Lakeのタイルアーキテクチャを下支えする「Foveros」という技術を解説するティム・ウィルソン氏(デザインエンジニアリンググループ バイスプレジデント兼SoCデザイン担当ゼネラルマネージャ)

少しややこしいのだが、Meteor Lakeにおけるタイルアーキテクチャは、「Foveros(フォベロス)」と呼ばれるダイ間積層配線技術によって実現している。

Foveros自体は全く新しい技術ではない。民生品向けとしては、2020年に登場したタブレットPC/2in PC向けCoreプロセッサ(開発コード名:Lakefield)で初採用されている。

しかし、このLakefieldは、レノボの初代「ThinkPad X1 Fold」など、幾つかのタブレットPCで採用はされたものの、採用事例は非常に少ない。そのせいか、量産開始から1年後の2021年には生産終了が告知されてしまった。Coreプロセッサファミリーの中でも、非常に短命な部類に入る製品だったともいえる。

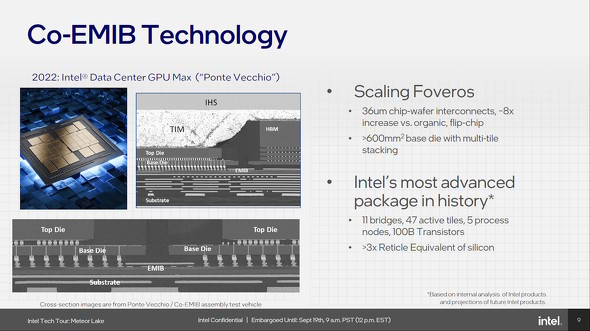

一度は消えたと思われたFoverosだが、Intelは「Intel Data Center GPU」(開発コード名:Ponte Vecchio)において再び採用し、量産実績を積み重ねてきた。

Ponte Vecchioでの実績を通して、IntelはMeteor LakeでもFoverosを“使える”と判断したのだろう。

では、Meteor Lakeのタイルアーキテクチャは、従来のチップレット技術と何が違うのだろうか。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Intelが次世代CPU「Meteor Lake」の概要をチラ見せ 全モデルに「AIエンジン」を搭載

Intelが次世代CPU「Meteor Lake」の概要をチラ見せ 全モデルに「AIエンジン」を搭載

Intelが「Meteor Lake(メテオレイク)」というコード名で開発を進めているCPUの概要情報を公開した。同社初の7nmプロセスCPUは、全モデルにCPUコアとは別体の「AIエンジン」を搭載するという。 Intelが次世代のクライアントPC向けCPU「Alder Lake」を2021年に投入

Intelが次世代のクライアントPC向けCPU「Alder Lake」を2021年に投入

Intelは8月13日(現地時間)、オンラインイベント「Intel Architecture Day 2020」を開催し、次世代のクライアント向け製品「Alder Lake」について発表した。 ついに! ようやく? 「Intel Maxシリーズ」2023年1月から出荷 HBM付き「Xeon Max」と高密度実装GPU「Intel GPU Max」

ついに! ようやく? 「Intel Maxシリーズ」2023年1月から出荷 HBM付き「Xeon Max」と高密度実装GPU「Intel GPU Max」

Intelが、HPC(ハイパフォーマンスコンピューティング)と機械学習ベースのAI(人工知能)用のCPU/GPUの統一ブランドとして「Intel Max」を立ち上げる。その第1弾製品はSappire Rapidsと呼ばれていたCPU「Xeon Maxプロセッサ」と、Ponte Vecchioと呼ばれていた「Intel Data Center GPU Max」である。 イスラエルのIntelハイファラボで見た“ちょっと未来”のPC像

イスラエルのIntelハイファラボで見た“ちょっと未来”のPC像

Intelはイスラエルに一大拠点を構えている。先日、報道関係者向けにその現状を伝えるツアーが開催されたが、今回は「Intel 8088」や「MMX Pentium」などを生み出したハイファにあるIDC(Israel Development Center)において実際に研究/開発された技術のデモンストレーションの様子をお伝えする。 最大6GHz駆動を実現! Intelが第13世代Coreに至る道のりをイスラエルで公開

最大6GHz駆動を実現! Intelが第13世代Coreに至る道のりをイスラエルで公開

Intelが“世界中の”メディアを集めてイスラエルの研究開発拠点「Israel Development Center(IDC)」の見学ツアーを開催した。その基調講演において、IDCが開発してきたCPUの歴史と、間もなく登場がうわさされる第13世代Coreプロセッサ(Raptor Lake)の近況が解説された。