携帯電話の高性能化を実現するフラッシュメモリアーキテクチャを発表

米Spansionは部品コストの大幅な削減と設計の柔軟性を高めることができる多機能携帯電話向けのメモリアーキテクチャを発表した。

米Spansionは4月4日、同社の複数のメモリ技術を単一のダイ上に集積することができる高機能携帯電話向けのフラッシュメモリアーキテクチャ「MirrorBit Eclipse」(Eclipse)を発表した。アプリケーションの高速化や製造コストを30%以上削減できるとしている。

Eclipseは、メモリ内のプログラムコード実行領域とマルチメディアなどのデータ保存・処理領域を自在に設定することができる。実装されるアプリケーションを基準にしてメモリ領域を割り当てられるため、携帯電話端末の設計の柔軟性が大幅に高まるという。

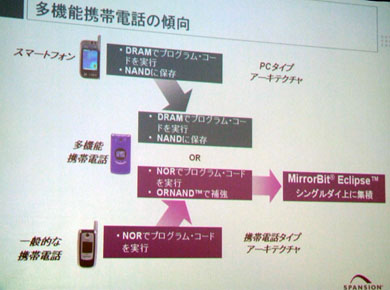

スマートフォンに代表される高機能端末では一般的にプログラム処理用のDRAMメモリとデータ処理用のNAND型メモリで構成されている。一方で、普及型端末ではデータへの高速アクセスに優れるNOR型フラッシュメモリが採用されている。

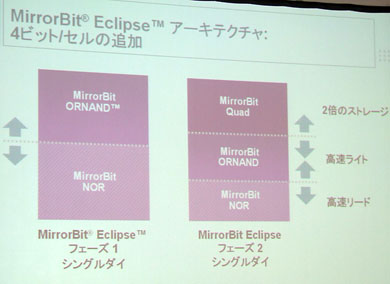

同社は、NOR型メモリを補完してプログラム処理を効率化する技術「MirrorBit NOR」と、書き込みも強化した「MirrorBit ORNAND」を提供してきた。

Eclipseは、NORやORNAND技術を基に発展させ、単一のダイでプログラム用領域とデータ用領域を提供できるようにした。このため、製造コストを30%以上削減できるという。既存のチップセットとの互換性も確保され、早期導入ができるメリットもあるとしている。

同社のバートランド・カンブー代表取締役社長兼CEOは、「従来からのNOR型のイメージを変えて、携帯電話のさらなる多機能化、高性能化を実現する革新的なアーキテクチャだ。マルチメディア端末やスマートフォン普及の著しい日本や韓国市場向けに展開を始める」と話す。

Eclipseは当初、65ナノメートルプロセスで製造され、2007年第3四半期にサンプル出荷を開始する。また2008年に45ナノメートルプロセスへ移行するとともに、4ビット/1セルの大容量を持つ「MirrorBit Quad」も集積できるようにする計画だ。「低コスト+高速処理」または「低コスト+大容量データ」といった、さまざまな携帯電話端末の開発ニーズに対応していくことにしている。

Copyright © ITmedia, Inc. All Rights Reserved.

アイティメディアからのお知らせ

人気記事ランキング

- なぜAI時代に「オンプレ」が復活? 2026年のITトレンドを占う

- 生成AIの次に来るのは「フィジカルAI」 NVIDIAが語る、普及に向けた「4つの壁」

- CVSSは「10.0」 ReactとNext.jsにリモートコード実行の脆弱性

- 10万超のWebサイトに影響 WordPress人気プラグインに深刻なRCE脆弱性

- 企業の半数以上がインシデントを経験 年末年始に潜むサプライチェーン攻撃の脅威

- Nintendo Switchのネットサービスさえ止めた「AWS障害」 CIOが得るべき教訓は?

- セールスフォースにも決められない? AIエージェント、「いくらが適正価格か」問題が勃発

- NEC 業務ノウハウを自動抽出、資産化するAIエージェントを提供開始 属人業務の行方は

- Accentureが“ChatGPT精通集団”に コンサル業務含め幅広く活用

- 7-Zipに深刻な脆弱性 旧バージョンは早急なアップデートを

バートランド・カンブー代表取締役社長兼CEO

バートランド・カンブー代表取締役社長兼CEO