DRAM待機電流を世界最小に エルピーダが新技術

» 2005年01月13日 17時17分 公開

[ITmedia]

エルピーダメモリは1月13日、DRAMの待機電流(セルフリフレッシュ電流)を世界最小レベルに抑える技術「SSR(Super SelfRefresh)テクノロジー」を開発、256MビットDDRチップに組み込んで製品化したと発表した。

DRAMは、データを保持するため定期的に電荷の再補充(リフレッシュ)が必要。リフレッシュ間隔を伸ばせばリフレッシュ電流を低減可能だが、その場合はデータエラーが出てしまうのが課題だった。

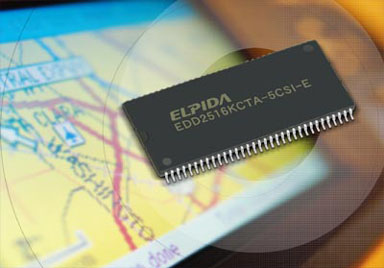

SSRでは、DRAM内部にエラー訂正回路を搭載し、リフレッシュ間隔を大幅に延長することで待機電流を抑える。新技術を組み込んで製品化した256MビットDDR「EDD2516KCTA」(DDR400対応)では、内蔵温度センサーによりリフレッシュ周期を自動調整。同社従来品の待機電力が3ミリアンペアだったのに対し、新製品は25度時に0.04ミリアンペアと従来比75分の1、70度時に0.15ミリアンペアと同20分の1に低減した。

新製品は既にサンプル出荷を開始し、3月から量産する予定。同チップを2枚使った512Mビット品も提供する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PRアイティメディアからのお知らせ

SpecialPR

あなたにおすすめの記事PR