RISCの実用性を証明した「MIPSアーキテクチャ」の誕生:RISCの生い立ちからRISC-Vまでの遠い道のり(1/3 ページ)

最近ではArm、RISC-Vなど組み込みでも華々しい活躍を見せているRISCプロセッサ。その祖先というか元祖として認識されているのはIBM 801というプロセッサだった。歴史的経緯を、IT史に詳しい大原雄介さんが解説する。

前回の記事で詳しくお伝えした、RISCムーブメントのきっかけとなったデビッド・A・パターソン教授らの論文である“RISC I:A Reduced Instruction Set VLSI Computer”(PDFへのリンク)が出た翌年となる1982年、今度は米スタンフォード大学のジョン・L・ヘネシー博士(当時の身分は電気工学とコンピュータ科学の助教授)らは、“MIPS: A Microprocessor Architecture”を1982年のACM SIGMICRO(コンピュータ科学の国際学会のマイクロアーキテクチャ分科会)で発表する。

このMIPS、今では処理性能の指標(Mega Instructions Per Second)として知られているが、この論文でいうところのMIPSは“Microprocessor without Interlocked Pipe Stage”(インターロックされないパイプラインを持つマイクロプロセッサ)の略である。区別を付けるため、こちらは俗に“Stanford MIPS”とも呼ばれる。

そもそもInterlockとは何かというと、「プロセッサの動作の一部分を一時的に止めること」である。例えばA=B+C(BとCの値を読み出し、合計をAに書き出す)の処理で、BとCがキャッシュに入っていなかったりすると、メモリからBとCを読み出す必要があるが、それには相応の時間が掛かる。なので、BとCをメモリから読み出すまでの間、演算はホールドしておく必要がある。この場合、メモリからデータを読み込む部分(昨今で言えばLoad/Storeユニット)だけは動いているが、それ以外の部分は一時的に停止(内部の状態は保持しつつ、処理を進めない)する必要がある。この状態をInterlockと呼ぶ。

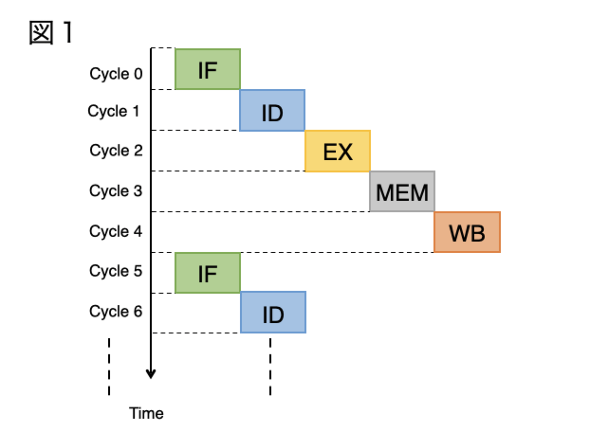

実際にはInterlockが起きる理由はたくさんある。最近のプロセッサでもデータハザードとかコントロールハザードは起き得るために、これを回避すべくいろいろな工夫が凝らされている(にもかかわらず根絶できない)が、1982年の段階のInterlockはもっと原始的な話である。MIPSの論文では5段のパイプライン構造を想定している。具体的には、

IF:Instruction Fetch(キャッシュから次の命令を取り込む)

ID:Instruction Decode(取り込んだ命令を解釈し、実行すべき処理を確定する)

EX:Execute(処理を実行する。メモリアクセスの場合には、そのアクセスすべきメモリのアドレスの計算を行う)

MEM:Memory(メモリアクセスを行う。といっても実際にはキャッシュへのアクセスであるが)

WB:WriteBack(処理完了に伴うレジスタファイルの開放を含む「後処理」を実行)

の5段階から構成されている(※1)。

※1:ここで説明したパイプラインは、その後インプリメントされたMIPSプロセッサに準拠する。当初の論文ではMEM/WBがなく、代わりにOD(Operand Decode)が入っており、またEXはOS/EX(Operand Store/Execution)とされていた。

話をInterlockに戻すと、この5段のパイプライン、従来は図1の様に実行されていた。まずIFが命令を1つFetchすると、その結果はIDに渡されるわけだが、渡し終わったあとのIFはInterlockが掛けられてそのままホールドされていた。というのは、IFの内部で解釈した結果をそのままIDで参照しているので、IFが変に動かれるとIDの動作に影響してしまうためだ。これはその先のEX/MEM/WBも同じで、なので各ステージ1サイクルで処理が終わったとしても、1つの命令の処理には5サイクルを要することになる。

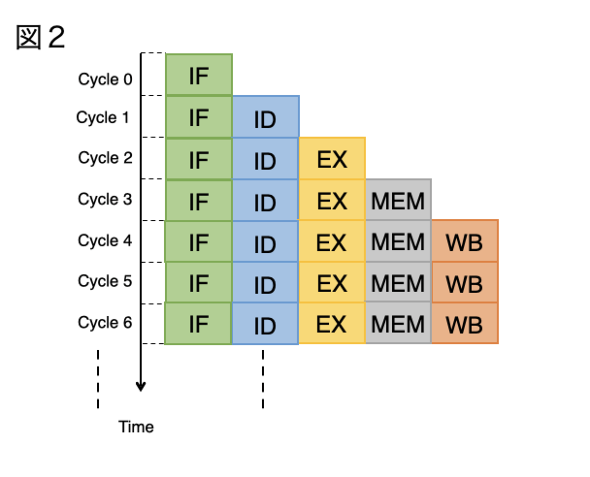

ヘネシー博士はこのInterlockを廃する仕組みを考えた。最初のサイクルでIFが1つ目の命令の取り込みを終え、その結果をIDに渡したら、即2つ目の命令の取り込みを行うようにすれば、各ユニットが並列して動作するようになる(図2)。

このケースだと、最初の命令を取り込み、それが書き戻されて完了するまで5サイクルかかる(これが実行のLatencyと呼ばれる)が、ただし命令そのものは1サイクル毎に各ステージへ順に取り込まれる(これが命令のThroughputと呼ばれる)ようになる。要するに5つのパイプラインステージを独立させて、Interlockを掛けないで処理できるように工夫するだけで、性能が5倍に上がるという仕組みだ。

この仕組みそのものは実はそれほど難しくない。要するに各ステージの間にバッファーを挟み、後段で参照するものは全てそのバッファーに保持するようにすれば、一度バッファーに保持した後は次の処理を始められることになる。ここで重要なのは各ステージの処理時間を均一にすることにより、無駄なInterlockを省くことができるというわけだ(処理時間が一定でないと、一番遅い処理時間のステージに合わせ、その他の処理ステージにはInterlockが掛かることになる)。

論文に戻ると、ヘネシー博士はBerkeley RISCの発想を下敷きにしつつ、これをベースにしていかに1チップで高速なCPUを構築できるかを論じている。主要な特徴、例えばメモリアクセスはLoad/Store命令に限り、その他の命令は全てレジスタのみを対象とするとか、命令レベルで複雑な処理をさせるのではなく、コンパイラレベルにそうした処理をオフロードするといった部分は共通である。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR