JEITAの半導体共同開発新プロジェクト、産学官で連携へ

NECエレクロトニクス、東芝、ルネサステクノロジなど国内企業10社で構成する電子情報技術産業協会(JEITA)・半導体幹部会は6月10日、2006年度以降の半導体共同研究開発プロジェクト計画案を明らかにした。

各社の開発コストを削減して得意分野への集中を促し、国内半導体産業の国際競争力を強化することが目的。90−65ナノメートルプロセスのSOC(System On Chip)設計技術確立に向けて2001年から推進してきた民間プロジェクト「あすかプロジェクト」が2006年に終了することを受け、半導体産業研究所(SIRIJ)に委託して検討を進めてきた。

同幹部会委員長でNECエレクトロニクス社長の戸坂馨氏は、あすかプロジェクトについて、「日本の半導体産業がSOCにかじを切るきっかけを与えたと」と評価。新プロジェクトでは、競争が激化する国際市場で先行するため、産業界に加え、大学と公的機関の参加による産学官の連携により、技術の実用化までのスピードアップを図る方針を打ち出した。

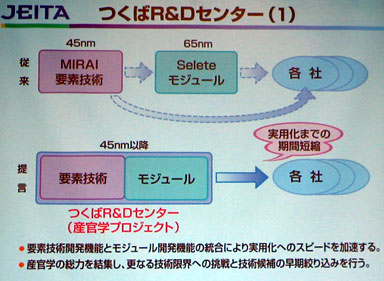

45ナノメートルプロセス技術の実用化のスピードを加速させるため、あすかプロジェクトの一部と、新エネルギー・産業技術総合開発機構(NEDO)が進める「半導体MIRAIプロジェクト」を協業させる。あすかプロジェクトでデバイスプロセスの技術開発を担っている半導体先端テクノロジーズ(Selete)のモジュール技術と、MIRAIプロジェクトの要素技術を有機的に結合。新設置する産学官共同プロジェクト「つくばR&Dセンター」で実用化をめざす。

同センターは、装置・材料メーカーにも参加を求めるほか、大学との連携も強める。同センターには強い管理権限を持つプロジェクトリーダーを設置する方針で、「リーダーは産業界から出したい」(JEITA半導体幹部会委員長・戸坂馨NECエレクトロニクス社長)。

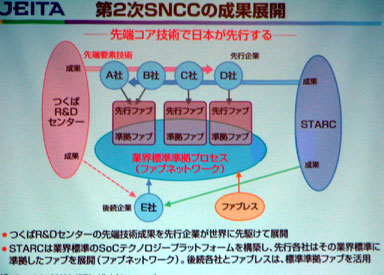

設計技術開発は、あすかプロジェクトで同開発を担当した半導体理工学研究センター(STARC)に集約。業界標準となるSOC設計方法論の開発を行なう。STARCでは、アプリケーション業界と協力して新市場創設を支援するほか、大学との連携も推進する。

これまで半導体メーカーに偏りがちだった基盤技術の研究開発を、産学官共同で推進することで、多面的な研究が可能になるとしている。

また、幅広い企業ニーズにこたえるため、コンソーシアムの運営構造も新しくする。リソグラフィー技術など先端技術の開発を行なう「先端コアプログラム」と、生産技術や解析・評価技術などさまざまな研究分野から、各企業が選んで参画できる「選択プログラム」を導入。各企業個別のニーズに合った効率のよい投資ができるようにする。

事業の研究成果は速やかに標準化。先行各社は標準に準拠した製造工場(ファブ)を展開し、複数工場からなるファブネットワークを形成する。先端技術を持たない企業やファブレス企業も、同ネットワークを利用して、先端技術を使った応用製品を生産できるようにする。

プロジェクト費用は、2006−2010年で総額1000億円規模になる見込み。参画各社への費用の配分は今後検討するとしており、「国からの援助も一部期待している」(SIRIJ第2次SNCC委員長の長澤紘一ルネサステクノロジ代表取締役兼CEO)。JEITAでは、来年3月末までの立案をめざしてSIRIJに具体的な計画の検討を委託する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR