48本のMPEG-2を同時デコード──Cellリファレンス:CEATEC JAPAN 2005

» 2005年10月04日 20時58分 公開

[小林伸也,ITmedia]

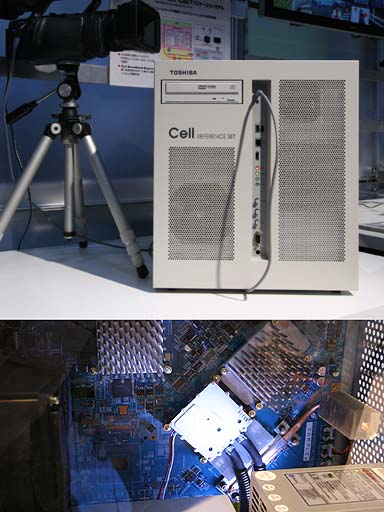

東芝は、「Cell」プロセッサを搭載したデジタル家電などを開発するためのリファレンスセットを公開した。MPEG-2を48ストリーム同時にデコードしてみせるデモなどを行い、Cellの高性能をPRした。リファレンスセットは2006年4月以降に発売する。

リファレンスセットのハードウェアは、Cellプロセッサとチップセットなどで構成。Cellと高速メモリ「XDRAM」とは、毎秒25.6Gバイトの「XIO」インタフェースで接続される。インタフェース全般を請け負うチップ「Super Companion Chip」とCellとは毎秒5Gバイトで接続。インタフェースはPCI-ExpressやギガビットEthernetなどのPC系と、デジタルチューナー入力やHDMI出力などのAV系を備える。

OSはITRONとLinuxをサポートし、開発環境はEclipseがベース。会場デモはすべてLinuxで行われた。

48ストリーム同時再生デモでは、720×480ピクセル(約4Mbps)のMPEG-2をHDDから同時に読み出し、6基のSPE(Synergistic Processing Elements)でデコード(1SPE当たり8ストリーム)。さらに7基目のSPEで画像サイズを3分の1に縮小し、HDTV上に並べて出力していた。

関連記事

- CEATEC JAPAN 2005特集

映像・情報・通信の総合展示会「CEATEC JAPAN 2005」が10月4日に開幕した。2005年のテーマは「発展するユビキタス社会。次が見える、明日が変わる」。約700社が出展して19万人超の来場が見込まれる。会場では、IT/電子分野における最先端技術、製品の展示が行われている。 - 東芝、Cellリファレンスセットを来春以降に発売

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PRアイティメディアからのお知らせ

SpecialPR

あなたにおすすめの記事PR

Cellリファレンスセットのマザーボード。ほぼ中央がCell、その左下が新開発のインタフェースチップ「Super Companion Chip」

Cellリファレンスセットのマザーボード。ほぼ中央がCell、その左下が新開発のインタフェースチップ「Super Companion Chip」 リファレンスセットの筐体(上)。Cellの冷却機構が見える(下)

リファレンスセットの筐体(上)。Cellの冷却機構が見える(下) 48ストリームのMPEG-2を同時デコードするデモ

48ストリームのMPEG-2を同時デコードするデモ デジタル1チャンネル、アナログ3チャンネルの同時録画デモ

デジタル1チャンネル、アナログ3チャンネルの同時録画デモ 来場者の顔の映像にリアルタイムに変化させるデモ。あらかじめ髪型とメイクアップのデータを用意しておき、来場者の頭の動きや表情に合わせて合成し、30fpsで出力する

来場者の顔の映像にリアルタイムに変化させるデモ。あらかじめ髪型とメイクアップのデータを用意しておき、来場者の頭の動きや表情に合わせて合成し、30fpsで出力する