RISCとCISCの境目がなくなる Pentium Proの逆襲:RISCの生い立ちからRISC-Vまでの遠い道のり(1/3 ページ)

最近ではArm、RISC-Vなど組み込みでも華々しい活躍を見せているRISCプロセッサ。その歴史的経緯を、IT史に詳しい大原雄介さんが解説する。

MIPSの成功は、多くのメーカーに路線変更を余儀なくされた。なにせMIPS R2000とこれに続くMIPS R3000は、あっという間に多数のワークステーションメーカーに採用されることになったからだ。そして自社でプロセッサを開発していたベンダーは、少なくともR3000を上回る性能を出せない限り、新製品の競争力が著しく劣ると見なされることを理解せざるを得なかった。

結果どうなったかと言えば、多数のメーカーが一斉にRISCプロセッサの開発に飛びつくことになる。Sun MicrosystemsはそれまでのMC68K路線を捨てて、自社でSPARCチップの開発をスタートする。HPは、それまでのHP-3000という独自アーキテクチャのCISCと、その後継になるはずだったFOCUSというプロセッサを、新しいPA-RISCに置き換え始める。DECはVAXチップの後継として、32bitのRISCチップであるPrismの開発を1982年にスタート、最終的にキャンセルされるものの、このPrismの遺産(?)は次のAlpha CPUに引き継がれるといった具合だ。

こうした動きはコンピュータメーカーに限った話ではない。IntelはIntel 860とIntel 960という全く異なる2種類のRISCプロセッサを同時に開発。前者はメインストリーム向け、後者は組み込み向け市場にそれぞれ投入される。AMDはAm29000という、Berkeley RISCに近い構成のプロセッサを、やはり組み込み向けに投入。MotorolaはM68000系とは別に、MC88000というRISCプロセッサの開発をスタートしている。ただこれらのRISCプロセッサは、おおむね成功したとはいえなかった。

Intel 860はある意味理想を追いすぎた構成で、確かにストイックな構成と高いピーク性能を誇っていたものの、プログラミングが超高難易度で、普通にCで書いただけでは最適化が足りない(Intelのエンジニアがアセンブラで最適化しても、ピーク性能の半分しか出なかったという話がある)という代物。Intel 960はそこそこに使いやすく、それなりの性能が出たものの、Intelのメインストリーム製品ではないという理由であっさり廃番になってしまった。Am29000も広く使われたものの、後述するAMDの戦略変更であえなく廃番。そしてMC88000は、欲張りすぎたためにマルチチップ構成になってしまい、それが理由でまるっきり性能が出ずに、ほとんど商業的成功を収められなかった。

Motorolaは加えて言えば、そうでなくても不足気味だったエンジニアリングチームが、68Kの開発と88Kの開発の両方に振り分けられてしまった結果、MC68040はなかなか完成せず(そのため初期の製品はプロトタイプ版のXC68040という型番で出荷されていた)、後継のMC68050はキャンセル。MC68060は1994年に発表されたものの、この時にはもう市場がなくなっていた。

もっともこの時期MotorolaはIBMからPowerPCのライセンスを受けて(というか、PowerPCそのものがIBMとMotorolaの共同開発という建前である)PowerPCベースの製品をリリースしていたから、Motorola自身にとってもMC68060は「要らない子」になっていたのはちょっとかわいそうな話ではある。

余談のついでに書いておけば、MotorolaはMC68000の命令セットのうち、RISC命令と親和性が高そうな一部の命令のみをサポートするRISCベースのColdfireというアーキテクチャも開発した。これである程度68Kのアプリケーションがそのまま、RISCのスピードで動作する、という良いとこ取りを狙ったものだったが、あいにくほとんど普及せず、PowerPCに押されるように消えて行ってしまったのは、個人的にちょっと残念であった。

話を戻そう。IntelはIntel 860/960を開発してはいたものの、x86を止めるつもりは全くなく、1989年にはIntel i486、1993年にはIntel Pentiumをそれぞれ投入する。i486はSingle Issue In-Orderながら、Decode部をi386までのMicroprogramからHard Wiredに置き換えることで(当時としては)極限まで性能を高めたもので、PentiumはIn-OrderながらSuperScalarを実装して、さらに性能を高めたものだ。

どちらも基本的にはCISCの枠の中で開発されてきたプロセッサである。ただ、これに続くPentium ProではRISCに舵を切ることになった。

このあたりについては、実は文献がある。ロバート・P “ボブ” コールウェル氏の“The Pentium Chnonicles”がそれである。コールウェル氏は1990年にIntelに入社。オレゴン州に新設されたマイクロプロセッサ設計事業部に配属され、新しいP6プロセッサ開発プロジェクトのシニア・コンピュータ・アーキテクトになり、まずは基本設計に携わることになった。

ちなみに前職はMultiflow Computerで設計エンジニアを務めていたが、同社は1990年に倒産。しばらくの職探しの時期を経て6月にIntelに入った形だ。さて、同氏の“The Pentium Chnonicles”であるが、かなり冒頭の“Betting on CISC”という節で「まだこの時点でRISC/CISC論争は決着していなかったが、個人的にはRISCのテクニックをCISCに持ち込むことが可能だと考えた。この場合、純粋なRISCに比べてエンジニアリング作業の増大やダイサイズの大型化によるコスト増の問題はあるが、これは量産効果で吸収できると考えた」としている。

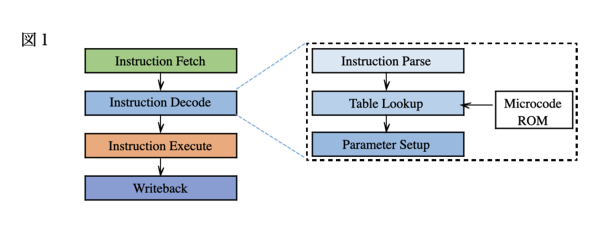

そんなことが可能か?というと、原理的にはそもそも難しい話ではない。図1は、従来型のCISCの内部をちょっと簡単に示したものだ。

Fetch→Decode→Execute→WriteBackという4段のステージから構成されているとする。問題はここのDecode段で、普通は、

- まず命令を分解して、どんな命令が来たかを理解する(Parse)

- その命令に相当するMicrocodeを、ROMから取得する(Lookup)

- Microcodeに必要なパラメータを追加して、Executeに引き渡す(Parameter Setup)

という形になっている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR