ナノテク領域での半導体プロセス開発を進めるインテル

昨日まで開催されていたIntel Developers Forum Japan Spring 2004で、インテルは、これまで発表していたナノテク時代の半導体プロセスについて、インテル・フェロー兼技術製造事業本部技術戦略担当ディレクタのパオロ・ガディーニ氏が説明した。

「半導体製造プロセスはすでにナノテクの領域に入っている」そうガディーニ氏は説明する。ナノテクの定義を“約1〜100ナノメートルの範囲で行われる原子、分子または高分子レベルでの研究および技術開発”とするならば、まさに現代の半導体製造技術はナノテクである。

配線ピッチ130ナノメートルのインテル製半導体の場合、トランジスタのゲート長は70ナノメートル。最新の90ナノメートルプロセスなら、ゲート長は50ナノメートルだ。いずれもナノテクの定義にピッタリ当てはまる。

もっとも、50ナノメートルと言われても普通はピンと来ることはない。インテルは毎回、その微細度を示すためインフルエンザウイルスとの比較写真をプレゼンテーションに用意している。インフルエンザウィルスの直径はちょうど100ナノメートル程度。最新のトランジスタサイズは、その半分にしか過ぎないことになる。

この進化の流れを止めないため、半導体ベンダーが開発しているのが、より抵抗の少ない配線材料の採用(近年、アルミから銅に変わってきた)や、絶縁皮膜の改良など新材料の開発と新材料をプロセス組み込むための研究・開発である。

また昨年、一昨年秋に米国で行われたIDFでインテルは、回路を露光させるためにEUV(極紫外線)と、マスクパターンで凹凸を付けた鏡を用いる、EUVリソグラフィーによる半導体製造に実験室レベルながら成功していることをアナウンスしていた。従来の露光装置では限界に近付いていた配線ピッチだが、この技術によって30ナノメートル以下の配線ピッチが可能になる。

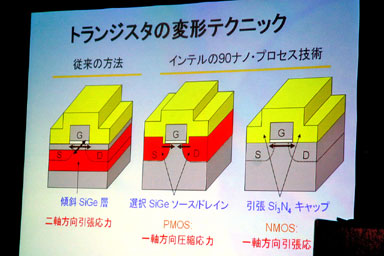

また、ナノテクを駆使し、より理想的なトランジスタをシリコン基板上に作り出す努力も、もちろん行っている。

たとえば歪みシリコントランジスタの実現だ。ガディーニ氏によると、シリコンの結晶に歪み与えて形状を変化させると、そのストレスで物理的なシリコンの構造がゆるみ、その中を電子が通りやすくなるという。その結果、トランジスタを駆動する電流が増え、高速な動作が可能となる。歪みを加えることで、10〜20%も電子の移動速度が速くなる。

「歪みシリコンはコストアップと言われるが、インテルのプロセスでは2%しかコストは上昇しない。しかも、漏れ電流は小さくなる」とガディーニ氏。

歪みシリコン・トランジスタを作るプロセスは、すでに90ナノメートルプロセスで実現済み。Prescott、Dothanとともに実際の製品に使われる。

もうひとつはゲート酸化膜の厚みだ。90ナノメートルプロセスにおいて、インテルはすでに1.2ナノメートルまで、酸化膜の厚みを減らしている。その写真を見ると、“原子”の数を簡単に数えられるほどの薄さだ。また近い将来、高誘電率(High-k)材料をゲート酸化膜に使えば、開発当初は現在より厚くなるものの、もっと薄い絶縁膜にできる可能性があるという。

High-k絶縁皮膜は、現在、エレクトロニクス業界全体が共有する問題として浮上している、トランジスタのリーク電流の問題を解決する切り札としてインテルが用意している技術だ。High-k絶縁皮膜を用いることで、リーク電流はインテルの90ナノメートルプロセスの1/100以下にまで下げることができる。High-k絶縁皮膜は2007年投入の45ナノメートルプロセスから採用されることが決まっている。

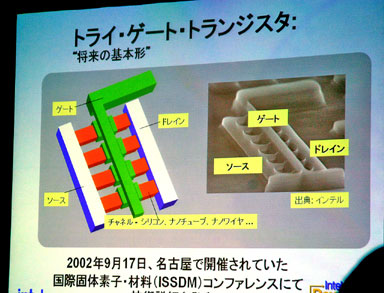

このほかガディーニ氏は、ナノテクレベルでの“理想的トランジスタ”の構築についても言及。シリコン上の立体的なトランジスタ構造を改善し、さらに3面にゲートを作るトライゲートトランジスタの製造に、2002年には成功していると話した。

トライゲートトランジスタは、製造プロセスが微細化する中でゲートを通過する駆動電流を増加させ、より高速に動作するトランジスタを作ることができる。「トライゲートトランジスタは、きわめて少ないリーク電流と、きわめて高い駆動電流を実現する」とガディーニ氏。

インテルはさらに今後、カーボンナノチューブやシリコンナノワイヤの利用を検討していく。現在の予定では、2013年に導入予定の16ナノメートルプロセスまでは現状のプロセスを進化させていくが、2015年予定の11ナノメートルプロセス、2017年予定の8ナノメートルプロセスではでは、シリコンナノワイヤの利用を前提とした計画になっている。

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR

フェロー兼技術製造事業本部技術戦略担当ディレクタのパオロ・ガディーニ氏

フェロー兼技術製造事業本部技術戦略担当ディレクタのパオロ・ガディーニ氏