NECエレが55ナノプロセスを開発、2007年内に量産開始

NECエレクトロニクスは12月5日、55ナノメートルのCMOSロジックプロセス技術を開発したと発表した。同社によると、同プロセスを実用レベルで開発したのは世界初。一般の65ナノメートル製品と比べ待機時電力を10分の1に低減でき、携帯電話向けLSIなど向けに2007年第4四半期からの量産開始を計画している。

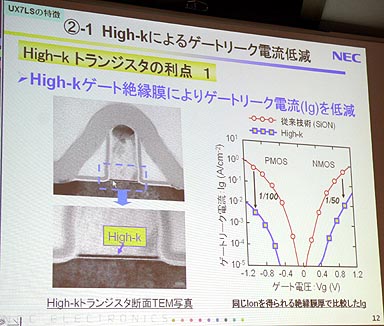

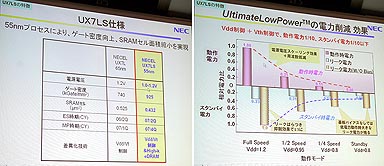

プロセスの微細化に伴い、トランジスタのリーク(漏れ)電流が性能向上と省電力化のボトルネックになってくる。同社の新プロセス「UIX7LS」(開発コードネーム)では、ゲート絶縁膜として高誘電率な「High-k絶縁膜」を形成。リーク電流を低減し、45ナノメートル世代と同等の高いトランジスタ特性を実現したという。

また基板バイアスを最大化するトランジスタ技術なども開発。一般的な65ナノメートルトランジスタに比べ、スタンバイ時の電力を10分の1以下に低減できる上、オン電流も20〜30%向上させた。DRAM混載も可能で、待受時間を長時間化できる携帯電話向けLSIやデジタル家電向けなどをターゲットに、省電力性能を売りに各社の65ナノメートル製品に対抗していく。

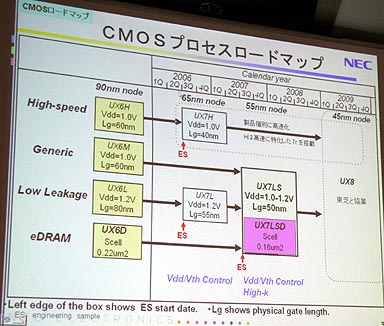

新プロセスによるサンプル出荷開始は2007年6月ごろを予定し、同年10〜11月にも量産出荷を始める計画だ。同社として初めて液浸リソグラフィー技術を導入し、NEC山形工場(鶴岡市)に対応ラインを設ける計画だ。液浸装置はオランダASML製と見られる。

新技術は、2004年にライセンス供与を受けた米Transmetaの省電力技術「LongRun2」(関連記事参照)をベースにしているが、「ASICにマッチする独立した技術」として開発したとしている。

同社は東芝と45ナノメートルプロセスの共同開発で合意しているが(関連記事参照)、DRAM混載技術など、製品の差別化できる技術については独自開発を続けていく考えだ。

関連記事

- 東芝とNECエレ、包括提携を検討 45ナノLSI技術を共同開発

東芝とNECエレクトロニクスが開発・生産で包括提携の検討を始めた。まず45ナノプロセスを共同で開発し、負担を分担して開発効率とスピードを上げる。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR

High-k絶縁膜として、ハフニウムシリケート膜をシリコン酸化膜の上層に積層する形で形成し、ゲートリーク電流を大幅に低減する

High-k絶縁膜として、ハフニウムシリケート膜をシリコン酸化膜の上層に積層する形で形成し、ゲートリーク電流を大幅に低減する

今後のロードマップ

今後のロードマップ