半導体チップに貫通電極 ASET、次世代実装技術でCCD試作に成功

技術研究組合・超先端電子技術開発機構(ASET)の超高密度電子SIプロジェクトは2月18日、半導体チップに貫通電極を設ける3次元実装技術を実用レベルで完成させたと発表した。この技術をもとにしたCCDモジュールの試作に世界で初めて成功し、従来製品よりモジュールを小さくできた。

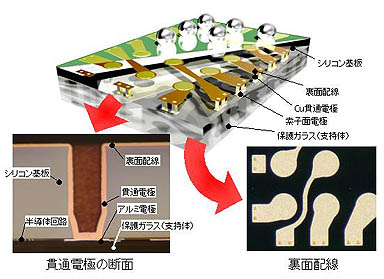

成功したのは、チップに貫通電極を設け、チップの表と裏に電極を形成する技術。チップの積層化に貢献する技術として各国で研究が進められていたもの。同プロジェクトは既に50μメートル厚のチップに20μメートルピッチの貫通電極を設け、4段積層する技術の開発に成功していた。

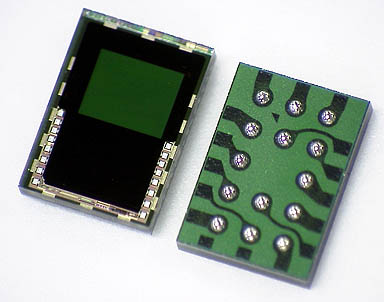

試作品の開発に当たり、組合員企業の三洋電機が市販CCDと同じウエハーを提供。開発した貫通電極プロセスを用い、厚さ150μメートルのウエハー裏面から50μメートル径の貫通電極を形成し、同プロセスによるCCDの試作に成功。市販品と同等の撮像結果が得られることを確認した。

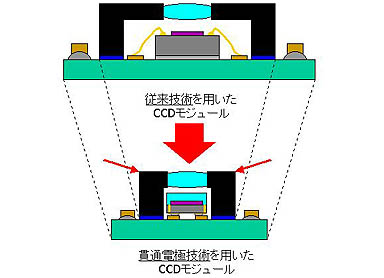

試作CCDは実装面積が約2.5×3.6ミリと小さく、CCD受光面の高さを約0.3ミリまで低くできる。このためレンズモジュールを細く低くでき、CCDモジュールを大幅に小さくすることが可能という。また貫通電極の配置を最適化することで、実装面積をさらに10%以上削減できるという。貫通電極によってワイヤボンディング配線が不要になるため、ウエハー支持体をCCD保護ガラスとしてそのまま用いることができ、プロセスの簡略化と信頼性の向上が可能だとしている。

同プロセスは既存のLSI設計やモジュール組み立てプロセスをほとんど変更せずに適用できる。ASETでは、同プロセスを応用した積層メモリチップや、新センサーモジュールなど、多くの応用製品の開発が期待できるとしている。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR

試作したCCD

試作したCCD 貫通電極プロセスによるCCDの構造

貫通電極プロセスによるCCDの構造 貫通電極プロセスによりCCDモジュールを小型化できる

貫通電極プロセスによりCCDモジュールを小型化できる