インクジェットで極薄20層フィルム基板 エプソンが世界初

セイコーエプソンは11月1日、フィルム上に20層の回路を積層した多層基板を、インクジェット技術を応用して世界で初めて試作したと発表した。電子機器の小型軽量化につながる上、従来方式と比べ、コストと環境負荷を抑えて高密度な多層基板を製造できるのが特徴。2007年度以降の実用化を目指す。

原理はインクジェットプリンタで紙に画像を印刷するのとほぼ同じ。数ナノ−数十ナノメートルの銀粒子を分散させたインクで、ベース材料に回路を“描画”することで配線し、その上に絶縁膜を塗布、また回路を描画──の繰り返しで多層基板を製造する。

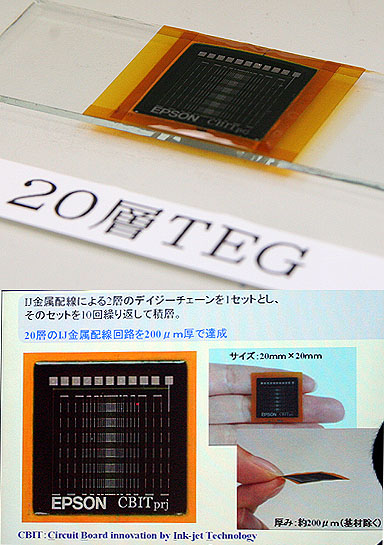

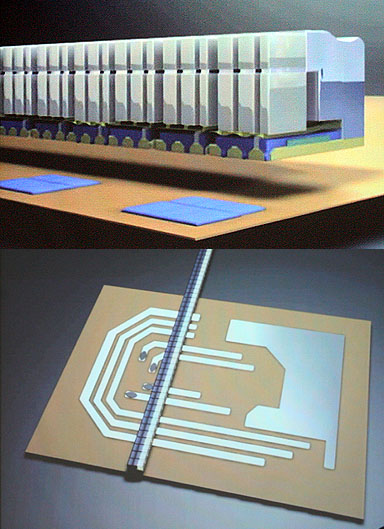

試作した20層基板は、40μメートルのフィルム上に20層の配線を重ねた。配線の厚さは4μメートルで、ベース部を除く厚さの合計は200μメートル。外形サイズは2×2センチで、総ライン長は5メートルに及ぶ。

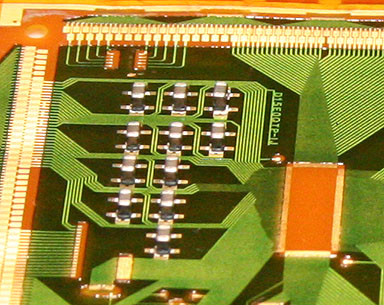

試作品の配線の幅は50μメートル、最小ピッチは110μメートルだが、現時点では幅は30μメートル、最小ラインピッチは70μメートルまで可能なことを確認した。基板上へのICチップ実装や半田付けによる素子実装、1枚のベースからの多数個取りも可能なことを確認済みだ。

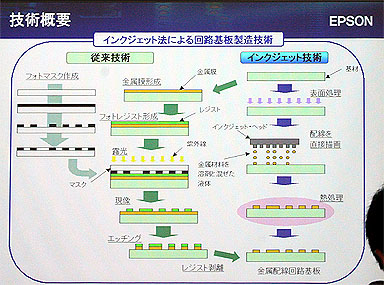

一般のプリント基板は、半導体などと同様にフォトリソグラフィ法で製造される。感光剤(レジスト)を塗布したベース基板上に配線マスク(フォトマスク)を重ねて露光し、現像、エッチング、レジスト除去などの工程を経て完成する。

これに対しインクジェット法の場合、必要な部分だけ描画するため材料使用量が少ない上、工程数を減らすことが可能で、工場の省スペース化や、現像液やエッチング液などの廃液が出ないなどのメリットがある。またフォトマスクを作成する必要がないため、多品種少量生産にも向く。

実用化では、フォトリソ法と比べコストを半減できるような用途での活用を想定して開発を進める。将来は回路配線とLSIチップなども積層した「システムインボード」や、製品本体に回路を描画する基板レス電子機器といった応用も進めていく。

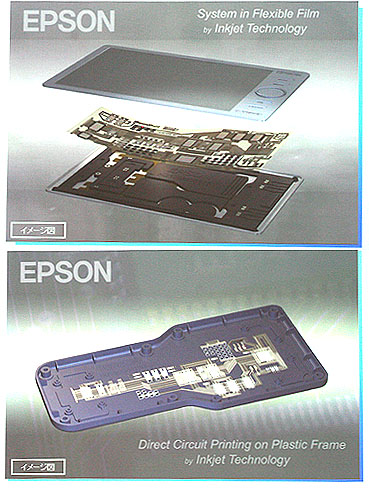

将来の応用例として、フィルム上にチップまで積層した「システムインフィルム」(上)や、製品のケース裏側に配線を形成する方法などを検討する。「インクジェット法は非接触なので、段差や曲面にも回路を形成しやすい」

将来の応用例として、フィルム上にチップまで積層した「システムインフィルム」(上)や、製品のケース裏側に配線を形成する方法などを検討する。「インクジェット法は非接触なので、段差や曲面にも回路を形成しやすい」新技術は、独立行政法人の新エネルギー産業技術総合開発機構(NEDO)の助成を受け、昨年6月から3カ年計画で開発を進めている。最終年の2006年度までに量産化のめどをつけ、翌年度以降からサンプル・量産出荷を計画している。

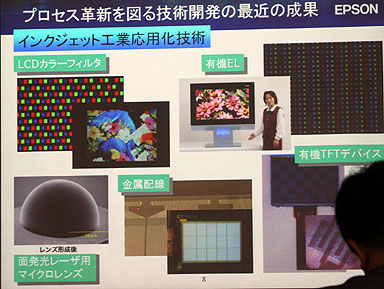

エプソンは、プリンタで培ったインクジェット技術の他分野への応用を積極的に進めている。5月には同技術による40インチ有機ELディスプレイの開発を発表している(関連記事参照)。

関連記事

- 「世界最大」の秘密は“高分子”と“インクジェット技術”――エプソン、40インチ有機EL

セイコーエプソンが開発した“世界最大サイズ”の40インチのフルカラー有機ELディスプレイ(OLED)は、高分子タイプの有機材料と同社独自のインクジェット技術を融合させることで圧倒的な大画面を可能にした。発表会では同社のテレビ事業も明らかに。 - エプソン、世界最大40インチの有機ELディスプレイ開発

セイコーエプソンが、世界最大サイズとなる40インチのフルカラー有機ELディスプレイ(OLED)を開発したと発表。2007年の製品化を目指す。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR

基板上に素子を実装したサンプル

基板上に素子を実装したサンプル 従来のフォトリソ法との比較

従来のフォトリソ法との比較 インクジェット法による基板製造のイメージ。おなじみのインクジェットヘッドが基板上を往復しながら金属配線−上下導通用ポスト−絶縁膜と描画を繰り返していく

インクジェット法による基板製造のイメージ。おなじみのインクジェットヘッドが基板上を往復しながら金属配線−上下導通用ポスト−絶縁膜と描画を繰り返していく インクジェット応用技術

インクジェット応用技術