Rambus、1テラバイト/秒のメモリバンド幅実現へ

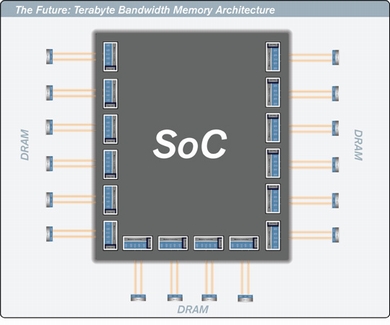

米Rambusは11月28日、1Tバイト/秒のメモリバンド幅を可能にする取り組みとして「Terabyte Bandwidth Initiative」を打ち出した。

同イニシアチブ実現のために、Rambusは「32X Data Rate」「Fully Differential Memory Architecture(FDMA)」「FlexLink C/A」の3つの次世代メモリ技術を推進する。

32X Data Rateは、1クロックサイクル当たり32ビットのデータ伝送を可能にする技術。従来のDDR(Double Data Rate)メモリでは1クロック当たり2ビットしかデータ伝送ができない。従ってDDRでは500MHzで1Gビット/秒のデータ伝送速度なのに対し、32X Data Rateでは、同じ500MHzのクロック周波数で、16Gビット/秒のデータ伝送を実現できる。

Fully Differential Memory Architecture(FDMA)では、データパスとコマンド/アドレスチャネルの両方に差動伝送を採用し、メモリコントローラとDRAM間の通信を改善する。差動伝送には干渉ノイズを軽減する効果があり、Rambusでは、これをデータ信号だけでなくコマンド/アドレス信号にも採用することで、信号品質の保持と性能の向上が達成できるとしている。

FlexLink C/Aは、ポイント・ツー・ポイント方式を採用したコマンド/アドレスリンク。これにより、DRAMとメモリコントローラの両方で、必要な信号ピンの数を減らすことができるという。例えば、1GビットDDR2ではメモリコントローラとDRAMのコマンド/アドレスリンクに28本のワイヤが必要だが、FlexLink C/Aでは2本のワイヤで16Gビット/秒のコマンド/アドレスリンクが可能だとしている。

関連記事

- FTC、Rambusへの「ロイヤリティ上限設定命令」の一部を猶予

米連邦取引委員会は、Rambusに対し、ライセンス供与時に相手企業に課すライセンスに上限を設定するよう求めていたが、この命令の一部が猶予となった。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR