RISCムーブメントが「IBM以外」で起きた、その理由:RISCの生い立ちからRISC-Vまでの遠い道のり(2/3 ページ)

86年といえば、既にMIPS R2000を搭載したワークステーションが1万ドル未満で購入できた時期であり、高いわりに性能の低いIBM PC RTには誰も見向きもしなかった。当時、ROMPの後継プロセッサも水面下では検討していたようだが、結局実現しないままで消え行くことになる。

ROMPそのものの後継ではなく、ROMPのアーキテクチャを基に作り直したのがPOWERプロセッサだが、その最初のPOWER1の最初のバージョン(RIOS-1)が完成したのは90年(ちなみに10チップ構成)で、そこから改良を重ねつつ、最終的に1チップ構成になったRSC(RISC Single Chip)が登場するのは92年。既にこの時点でRISCチップとしては後発になってしまっていた。

さて、前回の記事の最後に示した論文が世の中に出たのは2000年のことであるが、これに先んじてIBMのフェローだったジョージ・ラディン博士は“The 801 Minicomputer”という論文を83年に公開している。ただ、RISCのムーブメントはこれと全く異なるところから出現した。直接的なきっかけは、81年にUC Berkeleyのデビッド・A・パターソン教授とカルロ・H・セクイン教授が共著で出した"RISC I:A Reduced Instruction Set VLSI Computer"(PDFへのリンク)という論文である。

基本的な考え方はIBM 801におけるジョン・コック博士と同じであるが、パターソン教授はDECのVAX-11やPDP-11、IBMのSystem/38やSystem/3、それにIntelのiAPX-432やi8086を対象として利用される命令の頻度を調査した結果、こうした従来型(これをCISC:Complex Instruction Set Architectureと名付けた)のCPUでも、実際に利用されている命令はごくわずかであり、その割に複雑なために設計に時間がかかったり、設計にエラーが入り込んだりするとした。そこでCISCの対比としてRISC(Reduced Set Instruction Set)と呼ばれる新しい命令セットを提案した。

骨子は

- (1)全ての命令は1cycleで実行される(というか、全ての命令は1cycleで実行できるように設計する)。これにより複雑な回路実装が不要になり、回路規模を小さくできる。

- (2)全ての命令サイズを一定にする。これにより(プリフェッチが簡単になるので)回路を単純化できる。

- (3)メモリへのアクセスはLoad/Store命令に限り、その他の命令はレジスタアクセスのみとする。これにより命令体系が単純化され、複雑なアドレッシングが不要になる。

- (4)高級言語(論文ではCとPascalが挙げられた)のサポートを考慮する。

──の4つで、論文では実際にこの命令を実装したRISC Iという(この時点では仮想の)プロセッサをベースに議論が行われた。実際(4)を除くとコック博士のIBM 801と非常に似通った結論になっていることが分かる。もっとも(1)については、実際のIBM 801はインプリメントの都合もあってここまで徹底はできていないが、これはRISC Iがまだ仮想のプロセッサだったからこそという話もある。

このRISC Iは32bitアドレスと、8/12/32bitのデータタイプのサポート、32bit固定長のレジスタ、それとごく限られた命令の組み合わせで実現されることを想定していた。

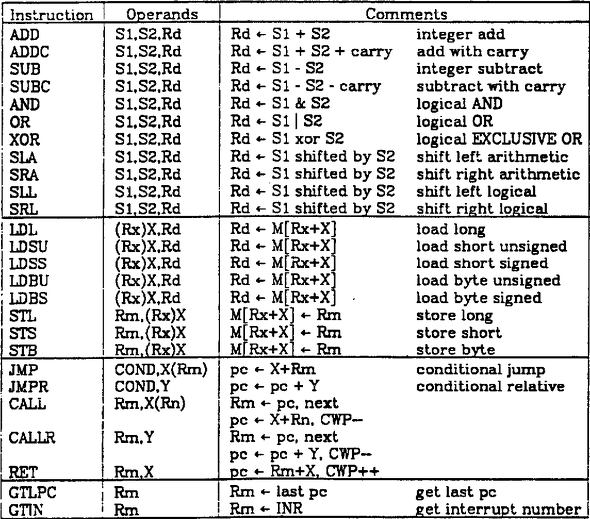

命令は4カテゴリーで合計26命令。浮動小数点演算は元より乗除算すらないが、シフト演算があれば組み合わせで乗除算は実現できるから、不要といえば不要ではある。商用というよりも研究プロジェクト向けCPUだからこそできた技ではあるが(出典は“RISC I:A Reduced Instruction Set VLSI Computer”のFigure 4)

命令は4カテゴリーで合計26命令。浮動小数点演算は元より乗除算すらないが、シフト演算があれば組み合わせで乗除算は実現できるから、不要といえば不要ではある。商用というよりも研究プロジェクト向けCPUだからこそできた技ではあるが(出典は“RISC I:A Reduced Instruction Set VLSI Computer”のFigure 4)汎用レジスタは全部で32個(R0〜R31)というあたりはIBM 801の初期バージョンと似ているが、R0レジスタをZero Register(常に値が0)に割り当てたあたりはちょっと異なる。またRegister Windowという概念を導入したのも新しい。これはProcedure Call(今で言えばFunction Call)を高速化するための技法で、昨今のRegister Renamingの元祖とでもいうべきものである。

RISC Iの場合、見かけ上32個のレジスタがあると書いたが、実際にはR0〜R9がGlobal、R10〜R15がLow、R16〜R25がLocal、R26〜R31がHighと4グループに分割されている。Globalはシステム全体で共通、LowはProcedure Callの際に呼び出し元がパラメータを格納し、Highは呼び出し先が結果などを格納する。そしてLocalはそれぞれが独自に利用してよいというエリアであるが、このエリアをRegister Windowのメカニズムを利用して自動的にSave/Restoreする(というか、呼び出し元と呼び出し先で、同じLocalを使っているように見えて、実際には異なる内部レジスタに割り当てる)というのがRegister Windowの仕組みである。

ちなみに論文によれば、レジスタを複数バンク持たせる実装は、例えばBBNのC/70などにも存在したらしいが、番号をオーバーラップさせる仕組みはない、としている。またIBM 801はBranch and Executeと呼ばれる仕組みを搭載していたが、RISC IもDelayed Jumpと呼ばれる仕組みを搭載している。

さて、論文ではこのRISC Iをシミュレーションした結果として、プログラムサイズそのものは60%前後増えるものの、処理速度は大幅に向上するとして論文を締めくくっている。

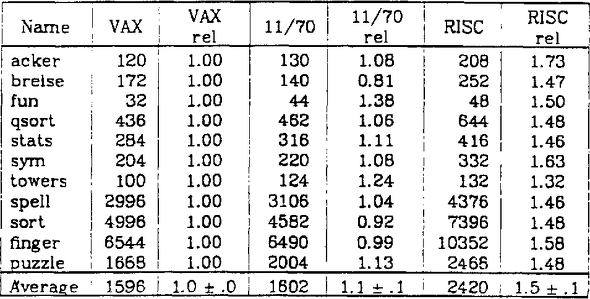

典型的な11のCのプログラムをVAX-11とPDP-11/70、それとRISC I向けにビルドした時の命令数を比較したもの。VAX-11とRISC IについてはUNIX portable C compilerを、PDP-11/70はRitchie C Compilerを使ったそうだ(出典は“RISC I:A Reduced Instruction Set VLSI Computer”のFigure 12)

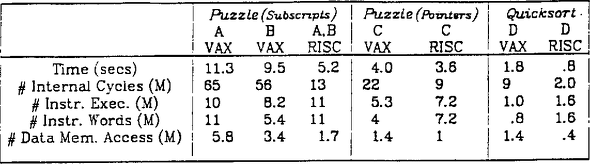

典型的な11のCのプログラムをVAX-11とPDP-11/70、それとRISC I向けにビルドした時の命令数を比較したもの。VAX-11とRISC IについてはUNIX portable C compilerを、PDP-11/70はRitchie C Compilerを使ったそうだ(出典は“RISC I:A Reduced Instruction Set VLSI Computer”のFigure 12) プログラムの実行サイクルとデータアクセス頻度が減った結果として、所要時間は多少ブレはあるもののVAX-11を下回るとした(出典は“RISC I:A Reduced Instruction Set VLSI Computer”のFigure 13)

プログラムの実行サイクルとデータアクセス頻度が減った結果として、所要時間は多少ブレはあるもののVAX-11を下回るとした(出典は“RISC I:A Reduced Instruction Set VLSI Computer”のFigure 13)Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR