RISCの実用性を証明した「MIPSアーキテクチャ」の誕生:RISCの生い立ちからRISC-Vまでの遠い道のり(2/3 ページ)

ただ、Stanford MIPSはBerkeley RISCと異なる特徴を持つことも論文には示されている。例えば、内部レジスタは16個の32bitレジスタで済ませていること、Berkeley RISCのRegister Windowは採用していないこと、レジスタの依存関係に起因するPipeline stallはコンパイラレベルでRe-organizer(命令発行順序を並び替える事で依存関係を解消する)を行わせること、当初からPage FaultやInterruptなどによる割込みの際に、Pipelineの退避/復活を意識していること、内部バスを命令とデータで分割し、それぞれを32bit幅で構成することでMemory Accessに起因するPipeline Stallを防止すること──などだ。

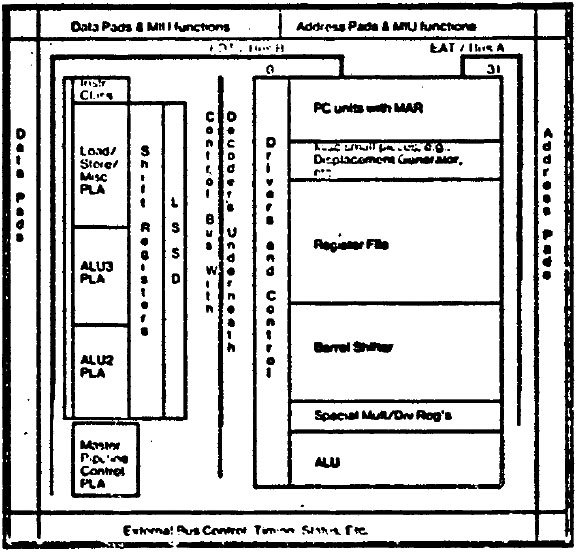

何よりも異なるのは、Berkley RISCでは「論文の後」でチップの製造が行われたが、Stanford MIPSについては「論文と並行して」チップの製造も行われていたことだ。実際論文にはチップのフロアプランまで掲載されている(写真2)。

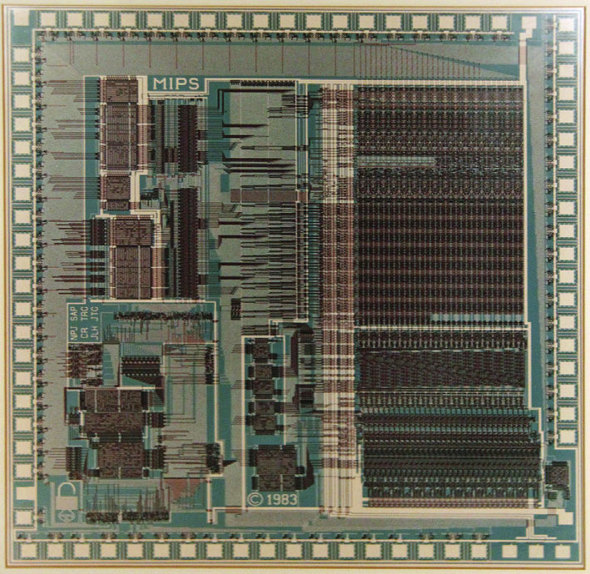

写真3:こちらはIEEE Micro July/August 2016に掲載されたA Retrospective on “MIPS:A Microprocessor Architecture”に掲載された写真より

写真3:こちらはIEEE Micro July/August 2016に掲載されたA Retrospective on “MIPS:A Microprocessor Architecture”に掲載された写真よりチップの製造には4μmプロセスを利用し、サイズは6.9mm×7.2mm。トランジスタ数は2万5000個と発表されている。論文によれば、シミュレーション上で動作するこのテストチップと、8MHz駆動のMC68000で同じベンチマーク(“Puzzle”という、当時広く利用されていたテストプログラム)を行ったところ、MC68000が実行に26.5秒要したのに対してテストチップは6.5秒で済んでおり、ここから逆算して4MHzのテストチップの性能がおよそ2MIPSの処理性能を持っているとしている(この当時、8MHzのMC68000の処理性能がおよそ1MIPS弱とされており、8MHzのテストチップが4.07倍ほどの性能を示したから4MIPS前後、4MHz駆動で2MIPSという計算になる)。これは、1982年当時としては画期的な性能だった。

ちなみに論文を書いた時点では6つのテストチップの設計が完了(今で言えばテープアウト)しており、このうち4つを製造工程に回したという段階であった。ただこの時点では全ての機能が盛り込まれていた訳ではなかったそうだ。この最初のMIPSプロセッサの設計が全て終わったのは1983年の春のことであり、1984年に最初のチップが出てきた(写真2)。

余談だが、この設計はスタンフォード大学内で教育や研究向けに開発や製造を行うCenter for Integrated Systems(現SystemX Alliance)で行われ、南カリフォルニア大学の試作半導体集積回路製造サービス(MOSIS)に製造委託したが、MOSISはこれを勝手にOptical Shrink(微細化)して製造したようで、結果3μm NMOSプロセス利用のチップが届いたそうだ。このチップを搭載した開発ボード上で、8-Queen(チェス盤の上で8つの女王を、お互いに取りあわないような位置に配するパズル)のプログラムが1984年2月20日に動いた、という逸話が残されている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR