RISC-Vの浸透 なぜRISC-Vが使われるようになったのか、その理由を探る:RISCの生い立ちからRISC-Vまでの遠い道のり(2/3 ページ)

命令セット周りでもう少し特徴を挙げておくと、

- 一貫した命令セット(32/64/128bitで基本的に差がない)

- 動作をPrimitiveなままに保つ

なども特筆すべきだろう。

まず前者、x86はそれでも8/16/32/64bitで互換性のある命令セットではあるが、それはニーモニックレベルで互換性があるという話であって、オペコードのレベルでは全く互換性がない。何しろもともと64bitアドレスまで拡張されるなんてことを考えずに8080で8bit向けに定義されたものを無理やり16/32/64bitに拡張したから、オペコードレベルで見ると無茶苦茶になっている。

Armなどは64bit(AArch64)導入時に全く新しい命令体系を導入したから、そもそも32bitと64bitでは全然別物になっている。これに比べて、基本的に命令に互換性があるRISC-Vは、インプリメントが相対的に容易である(もちろんこれは命令を実装するエンジニアとかコンパイラを作るエンジニアにとってのメリットでしかなく、普通にRISC-Vを使うソフトウェアエンジニアには関係ない話だが)。

後者は以前こちらでも触れた話だが、例えばADD(加算命令)は、条件分岐を後で行えばオーバーフローは検出できるので、ADD命令そのものにオーバーフローのチェック機構は入れないという具合に、どうしても他の命令で代替できないものしかそれぞれの命令では処理しないようになっている。

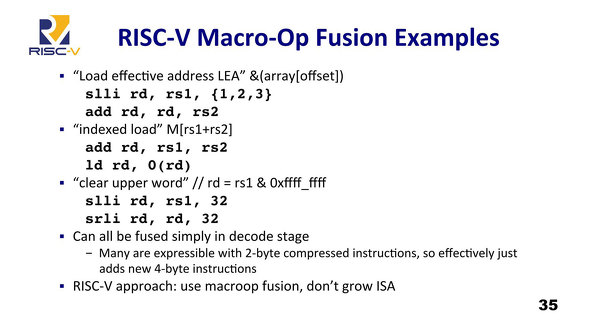

アセンブラで記述しているとこれは結構しんどい話であるが、高級言語だと自動的にそうした処理はコンパイラが適切なコードを出してくれるうえ、昨今のハードウェアの実装だとMacro-Op Fusion(複数の内部命令を組み合わせて1つの命令として実行する)ことが多いから、命令セットはシンプルなままに保つ方が良い、という考え方だ(写真4)。

写真4:もちろんMacro-Op Fusionを利用しなくても構わないが、その場合は性能でのペナルティーが発生する。どの程度Macro-Op Fusionを行うかで性能が変わってくる訳で、これがまたコアの差別化要因となる訳だ。出典はRISC-V Tokyo 2017におけるカーステ・アサノビッチ教授の“Instruction Sets Want to be Free!”

写真4:もちろんMacro-Op Fusionを利用しなくても構わないが、その場合は性能でのペナルティーが発生する。どの程度Macro-Op Fusionを行うかで性能が変わってくる訳で、これがまたコアの差別化要因となる訳だ。出典はRISC-V Tokyo 2017におけるカーステ・アサノビッチ教授の“Instruction Sets Want to be Free!”こうした割り切り方は、x86やArmに比べるとずっと新しいものであり、プロセッサベンダーにとっても他社のコアとの差別化要因を出しやすいポイントともなる訳で、当然これは歓迎すべき部分である。

2つ目の「実装が容易」はいくつかの項目に跨っている。まず上でも述べたように、RISC-VはBase Instructionを絞ることで、取りあえず最小構成のCPUを作るのは容易となっている。もちろん実際には上で書いたG(IMAFDの組み合わせ)が、商用プロセッサとしては最低限のレベルにはなると思うが、それでもそれほど複雑な命令セットではない。

これに加えて、RISC-VではChisel(Constructing Hardware in a Scala Embedded Language)と呼ばれるハードウェア記述言語が利用できる、というと語弊があるかもしれない。ChiselはUC Berkeleyで開発されたハードウェア記述言語で、抽象度という意味ではVerilogとかVHDL(どちらもASICとかASSP、FPGAなどの回路を記述するプログラミング言語)などと記述のレベルは大きくは変わらないが、Scala言語(最近人気のコンピュータプログラミング言語の一つ)をベースにしており、Scalaに慣れているエンジニアには取っつきやすいらしい(筆者も眺めてみたが、いまひとつ実感はない)。

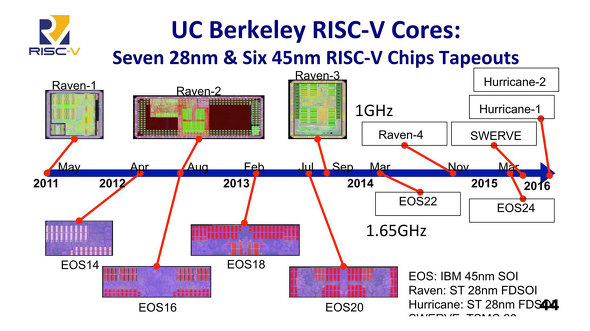

そのChiselだが、Ravenの設計に利用されたことで一躍有名になった。実際UC BerleleyではRaven-1だけでなく、2011年〜2016年にかけて合計13ものCPUを設計している(写真5)が、こんなことが可能になった理由の一つはChiselによって比較的容易にCPUの設計ができるようになったことだ(この後もTSMCの16FFやGlobalFoundriesの14nmをターゲットに、Craft、Broom、Eagleなどが設計されている)。ちなみにChiselそのものは汎用であり、Googleはエッジ向けTPUの設計にChiselを使ったことを2018年に発表している。

写真5:Taped Outというのは、設計完了を意味する。これは単に論理設計だけでなく、実際にFabで製造に利用するマスクを構築できるレベルで物理設計も終わった段階である(実際に作るかどうか、はまた別の問題)。出典はRISC-V Tokyo 2017におけるカーステ・アサノビッチ教授の“Instruction Sets Want to be Free!”

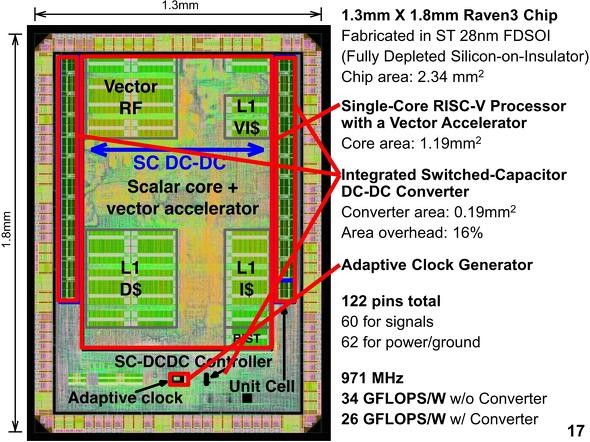

写真5:Taped Outというのは、設計完了を意味する。これは単に論理設計だけでなく、実際にFabで製造に利用するマスクを構築できるレベルで物理設計も終わった段階である(実際に作るかどうか、はまた別の問題)。出典はRISC-V Tokyo 2017におけるカーステ・アサノビッチ教授の“Instruction Sets Want to be Free!”Raven-3は後述のRocketコアを搭載、STMicroelectronicsの28nm FD-SOIプロセスで実際に製造され、Raven-1を上回る26GFLOPS/W(内部に搭載したDC/DCコンバーターを抜きにすれば34GFlops/W)を実現している(写真6)。

写真6:Raven-3もRaven-1の延長で高効率を狙った(ただし初代Ravenよりも汎用的に使える)設計である。ただここでの工夫は、むしろSoCに内蔵したSC(Switched Capacitor)DC-DCコンバーターと、20ns周期での調整を行うDVFS(Dynamic Voltage Frequency Scaling)辺りがメインであり、論文もこちらに力点を置いたものになっている。出典はHot Chips 27の“Raven: A 28nm RISC-V Vector Processor with Integrated Switched-Capacitor DC-DC Converters and Adaptive Clocking”(PDFへのリンク)

写真6:Raven-3もRaven-1の延長で高効率を狙った(ただし初代Ravenよりも汎用的に使える)設計である。ただここでの工夫は、むしろSoCに内蔵したSC(Switched Capacitor)DC-DCコンバーターと、20ns周期での調整を行うDVFS(Dynamic Voltage Frequency Scaling)辺りがメインであり、論文もこちらに力点を置いたものになっている。出典はHot Chips 27の“Raven: A 28nm RISC-V Vector Processor with Integrated Switched-Capacitor DC-DC Converters and Adaptive Clocking”(PDFへのリンク)Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR