RISC-Vの浸透 なぜRISC-Vが使われるようになったのか、その理由を探る:RISCの生い立ちからRISC-Vまでの遠い道のり(1/3 ページ)

前回はRISC-Vの基になるRaven-1に至るまでのUC Berkeley(米カリフォルニア大学バークレー校)の歴史を中心にご紹介したが、今月はそのRISC-Vのエコシステムが立ち上がるまでについてご紹介する。

ただその前に前回の記事に対する感想ツイートの中でちょっと気になったことがあったので補足など。

「低消費電力化にISAは基本的には関係ないのでは?」という指摘であるが、原則はその通り。いや厳密にいえば関係あるのだけど、普通は省電力の仕組みの中で、ISA(命令セットアーキテクチャ)がそれに関係する割合は無視できるほどに小さいというべきか。これもいろいろ言い始めるとキリがない(例えばVAXの多項式演算であるPOLYF命令など、処理サイクルがあまりに長いため、命令実行の途中で割込みが入った場合には、POLYF命令を途中で中断してISRを呼び出し、終わったら中断したところからPOLYF命令を再開できるなんて代物で、こういう命令をISAに組み込んでしまうと、不必要にそれをサポートするためのメカニズムが増えるので省電力には不向きとか、他にもいくつか思い付く)のだが。

ただ記事3ページ目の冒頭で書いた話はもっとシンプルな議論である。

Raven-1は極端な話、LINPACKベンチマークが効率よく動き、あと最低限OSとかモニターの類が動作すればことが足りるわけで、すると8bit演算命令とか16bit演算命令とかは実際問題として必要ない。こうした不要な命令を実装するためには設計の時間もかかるし、使われないロジック(デコードだけでなく、命令実行部、バックエンドにも8/16bitで動作するための配慮が必要)が入る。FD-SOI(完全空乏型シリコン・オン・インシュレータ)を使ったからといって、こうした使われないロジック部の消費電力を0にすることはできない(圧倒的に少ないとはいえリーク電流は発生する)し、余分なロジックが入るということはその分「ダイサイズも大きくなる」=「配線長が伸びる」=「配線遅延に起因する消費電力も増える」ということになる。

だから、できれば必要な命令だけを実装することにしたい。にもかかわらず、x86やArm ISAを利用すると、「自分が必要な命令だけを実装する」という選択肢はとれない。それを許すと互換性が失われるからだ。つまり互換性を取って、無駄なロジックを実装することで開発コストを引き上げ、しかも消費電力を増やすか、互換性を捨てて低コストで不要な消費電力を削減したプロセッサを作るのかという選択肢になる。Raven-1は超高効率なプロセッサを開発するのが目的であり、互換性を維持する必要はなかったから後者を選んだというわけだ。

ちなみに筆者はプロセッサの設計経験はない(ハードウェアの設計経験はある)が、互換性を無視して極限まで消費電力を抑えたいという目的のために、ISAに手を入れるのは別に不思議ではないと思う。

さて本題。前回の最後で、新しいISAがマーケットを獲得する条件として、

- ISAそのものが魅力的であり、安価(可能なら無償)で入手できること

- 実装が容易であること

- ソフトウェアのサポート

の3つを掲げた。

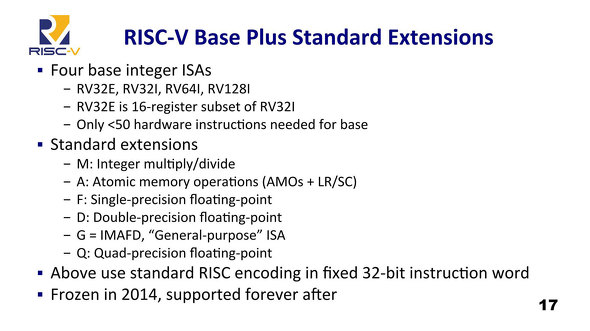

RISC-Vはこれを忠実に実現した。まず命令セットについて。RISC-VはBase Instruction+Extensionという形をとる。このうち必須命令となるのは全部で47命令ほどのBase Instructionで、RISC-V互換を名乗るためにはこのBase Instructionの実装は必須である。

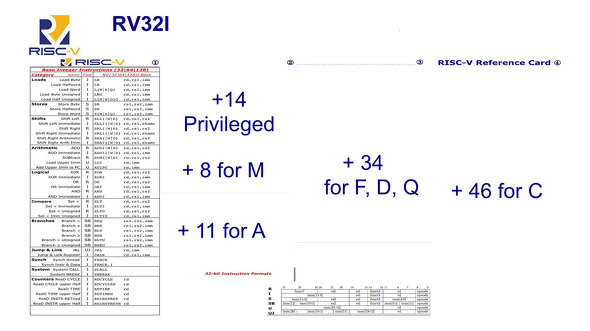

ただ命令セット一覧(写真1)を見ていただくと分かるが、このBase Instructionに含まれているのは本当に最小限であり、命令セットも32bitの固定長となっている(写真2)。

写真1:基本となるのはRV32I(32bitアドレス)で、MCU向けのサブセットがRV32E、64/128bitアドレスを持つのがRV64I/RV128Iである。出典はRISC-V Tokyo 2017におけるカーステ・アサノビッチ教授の“Instruction Sets Want to be Free!”

写真1:基本となるのはRV32I(32bitアドレス)で、MCU向けのサブセットがRV32E、64/128bitアドレスを持つのがRV64I/RV128Iである。出典はRISC-V Tokyo 2017におけるカーステ・アサノビッチ教授の“Instruction Sets Want to be Free!” 写真2:このシンプルさはBerkeley RISC-Iの命令セットにも通じるものがある。ただ商用プロセッサ向けということを考えて、論理演算とかThread同期とかをBase Instructionに含めたのはさすがというべきか。出典はRISC-V Tokyo 2017におけるカーステ・アサノビッチ教授の“Instruction Sets Want to be Free!”

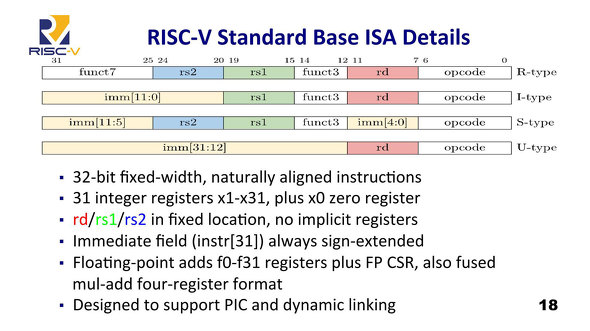

写真2:このシンプルさはBerkeley RISC-Iの命令セットにも通じるものがある。ただ商用プロセッサ向けということを考えて、論理演算とかThread同期とかをBase Instructionに含めたのはさすがというべきか。出典はRISC-V Tokyo 2017におけるカーステ・アサノビッチ教授の“Instruction Sets Want to be Free!” 写真3:R/I/S/Uは、写真2の中段のFmt(Format)カラムの指定に準拠する。出典はRISC-V Tokyo 2017におけるカーステ・アサノビッチ教授の“Instruction Sets Want to be Free!”

写真3:R/I/S/Uは、写真2の中段のFmt(Format)カラムの指定に準拠する。出典はRISC-V Tokyo 2017におけるカーステ・アサノビッチ教授の“Instruction Sets Want to be Free!”Berleky RISC-Iよりは若干命令セットが複雑ではあるが、それこそArmとかx86とは比較にならないほどシンプルな構成だ。このBase Instructionは2014年にフィックスされており、その後の変更は一切行われないことになっている。

これだけだと実装は楽だが、魅力的かどうかと聞かれれば足りないものが多すぎる。これをカバーするのがExtensionで、写真1にも出ているがM(整数乗除算)、A(アトミック命令)、F(単精度浮動小数点演算)、D(倍精度浮動小数点演算)、Q(4倍精度浮動小数点演算)であり、もともとのI(基本整数演算)と合わせてIMAFDの組み合わせをG(General Purpose ISA)としている。

ちなみに他にはL(10進浮動小数点:未定義)、C(圧縮命令フォーマット)、B(ビット操作命令:審議中)、J(動的変換命令:未定義)、P(Packed SIMD:審議中)、V(Vector SIMD:審議中)、N(ユーザーレベル割込み:審議中)、H(ハイパーバイザー拡張:未定義)、S(スーパーバイザ対応命令:審議中)などがExtensionとして挙げられている。

2019年のRISC-V Dayでは台湾のAndes TechnologyがP Extensionについていろいろ説明を行っていたが、こうした命令拡張はRISC-V internationalに加盟してワーキンググループに参加することで、誰でもこの命令拡張に関する議論に参画できるし、何なら自分で考えた命令拡張を提案することもできる。

加えていうならば、それこそ前回の記事の冒頭で述べたような、研究目的で命令セットをいろいろいじりたいといったケースでは、Base instructionに手を入れても構わない。もちろん手を入れてしまうとそれはRISC-Vとは呼べないし、RISC-V対応のToolchainが利用できなくなるといったデメリットはあるが、別にそうしたカスタマイズを自分で行い、自分で責任を持つ分には自由である。

Armやx86のように、そうした命令セットを作ると訴えられるような危険性はない。こうした形で豊富な命令セットと自由度を両立したのがRISC-Vの特徴である。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR