UMAからの脱却 そしてNUMAに入る:“PC”あるいは“Personal Computer”と呼ばれるもの、その変遷を辿る(2/4 ページ)

スケールアップ問題

まぁここまでは普通の話である。Pentium以降のIntelやAMDのCPUは全部こんな感じでマルチプロセッサシステムを構成していたし、それ以前にマルチプロセッサ構成を構築したCompaqのSystemPro(写真1)とか、Corollaryがチップセットを提供したZenith Data SystemsのZ-1000(386+387のセットを最大5組搭載できるServer:1988年発表)も似たようなもので、メモリは1カ所に集中していた。要するにUMAのままだ。この方式を取る限りは、データの整合性とかを考える必要はない。

写真1:Compaqが1989年に発表した、386ベースのDual Processor ServerであるSystemPro。独自のFlex Architectureと呼ばれる内部バス構成であるが、メモリ構成そのものはUMA。ちなみに翌1990年には486ベースの構成も発表された(CPUそのものがドーターボードに搭載されている構成だったので、簡単に置き換えが可能だった)

写真1:Compaqが1989年に発表した、386ベースのDual Processor ServerであるSystemPro。独自のFlex Architectureと呼ばれる内部バス構成であるが、メモリ構成そのものはUMA。ちなみに翌1990年には486ベースの構成も発表された(CPUそのものがドーターボードに搭載されている構成だったので、簡単に置き換えが可能だった)問題はこの方式がスケールアップにまるで向かないことである。図2で、CPUとMemory(というかChipset)をつなぐInterconnect、2 CPUくらいならそれほど問題無いが、4 CPUともなると、

- 4つのCPUからのメモリアクセスを1カ所のメモリコントローラで処理することになり、メモリ帯域がボトルネックになる。

- それ以前にInterconnectが共有バス形式なので、速度が上げにくくなっており、こっちが先にボトルネックになることもしばしばある。

という問題が出てくる。

IntelはPentium 4 Xeonで、力業の解決案を示した。4P対応のXeon MPでは、FSBを400MHzでしか稼働させられなかったため、2MBのL3キャッシュを追加(のちに4MB版も追加)してこれをカバーするという方策である。

ただキャッシュにHitしている間はともかく、キャッシュミスが多発する様なアプリケーションではFSBの遅さとメモリコントローラの競合のお蔭で大幅に性能が落ちることになったのは、構成を考えれば致し方ない。

この問題に対して最初にソリューションを示したのは、1983年に設立されたSequent Computer Systemsである。

同社の最初の製品はNS32032を12個搭載するマルチプロセッササーバで、この時点ではまだUMA構成であったが、その後x86にプロセッサを入れ替え、Symmetry S81では80386×30、続くSymmetry 2000/700では80486×30、さらにPentiumベースのSymmetry 2000/790ではPentium×30とかの構成のサーバを投入していた。

ただこのあたりから同社はUMA方式の限界に到達したと判断したようで、このあと同社はこれまで築いてきたUMA+SMPの方式をIntelにライセンス供与する(Pentium Pro以降で4P構成が可能になったのは、このSequentのライセンスに拠るところが大きい)。

その一方で自社はccNUMAのアーキテクチャを導入する。このccNUMAの技術を開発したのはChen Systemという会社であるが、SequentはこのChen Systemを1996年に買収、同社が持っていたccNUMAの技術をNUMA-Qという名前で商品化している。

NUMAとは何か?というと、メモリコントローラを分散させる仕組みである。“Non” Uniform Memory Architectureというのは、メモリの置き場所が複数あり、別々に管理されているという話である。

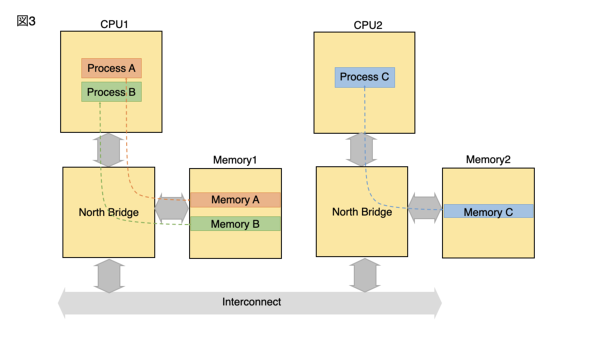

図3がその最初のNUMAの構成であり、CPU 1で動くProcess A/BはMemory 1内にメモリアドレスを割り当て、一方CPU 2で動くProcess CについてはMemory 2内にメモリアドレスを割り当てるようにすれば、効果的に使えるようになるというものだ。

実際図3のような構成であれば、Interconnectに無駄なトラフィックは発生しないし、メモリコントローラがボトルネックになることもない。CPUの数が増えても、それに対応するだけメモリコントローラを増やせれば、性能はスケールさせやすいことになる。

実際SequentのccNUMAを最初に搭載した製品は、最大128枚のCPU Blade(CPUとNorth Bridge、メモリコントローラを搭載した基板)を組み合わせ可能な構成になっていた(ただしこれはSequentの時代ではない)。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR