AMD、次世代APU「Carrizo」のアーキテクチャ詳細を明らかに:処理能力もバッテリー駆動時間も“二桁”アップ

半導体開発者国際会議「ISSCC」で現在開発中のCarrizoの構成と機能を公開した。構成トランジスタ数は従来の29%増、実装する動画圧縮エンジンは2倍に及ぶ。

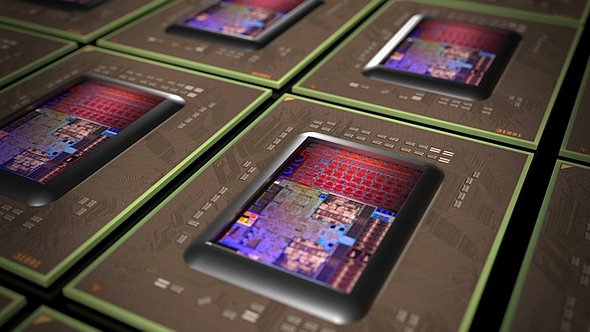

AMDは、2月24日にAPU Aシリーズの次世代モデル「Carrizo」(開発コード名)の詳細を明らかにした。Carrizoは、最新世代のCPUコア「Ecavator」とRadeonシリーズのグラフィックスコアを統合した、HSAに対応する初めてのAPUとなる予定だ。

Carrizoでは、前世代APU「Kaveri」と同じサイズのダイサイズながら、構成トランジスタ数が29%増えて31億個となった。サウスブリッジシステムコントローラもAPUに統合する。

統合するグラフィックスコア「Radeon」も新世代となって専用の電源を備えたほか、H.265デコード用の専用エンジンも実装する。このことで、Carrizoは4Kクラスの動画再生に対応できる。また、動画圧縮エンジンの数はKaveri世代と比べて2倍になったという。

これらの改変によって、処理性能、そして、バッテリー駆動時間はともに“二桁”の向上を実現。強力な電源管理機能によってCPUコアの消費電力を40%削減しながらも、処理能力は大幅に向上するとAMDは説明している。

従来の電力管理では、電圧が一時的に低下する「ドループ」減少に対応すべく、10〜15%の余剰電圧を供給していたが、Carrizoの新しい電力管理技術では、CPUコアとグラフィックスコアの両方において、10億分の1秒単位で平均駆動電圧をチェックすることで、効率的にドループ減少に対応できるようになり、電力消費量がCPUコアで最大19%、グラフィックスコアで最大10%削減できる。

加えて、「AVFS」(Adaptive Voltage and Frequency Scaling)という技術では、電圧センサと「シリコン・スピード・ケイパビリティ・センサ」を用意して、APUに実装するシリコン特性、プラットフォームの挙動、そして、運用環境に合わせた制御ができるようになった。APUの稼働状況と負荷変化に動的に対応することで、電力消費を最大30%削減できる。

さらに、28ナノメートルプロセスルールと限られた電力供給でも処理能力が確保できるようにグラフィックスコアの実装をチューニングすることでも、電力効率の改善を図っており、Kaveriの統合グラフィックスコアと比べて同じ動作クロックで最大20%の電力削減を可能にしている。

なお、PC USERでは、ISSCCに合わせて明らかになったCarrizoアーキテクチャの詳細な“大解説”を後日掲載する予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

“Excavator”採用のAMD新世代APU「Carrizo」を掘り下げる

“Excavator”採用のAMD新世代APU「Carrizo」を掘り下げる

AMDがシンガポールで行ったプライベートイベントでは、2015年に投入する新技術の発表や、2020年を目指した開発目標をアピールした。 次期APU“Carrizo”の概要が明らかに──「Future of Compute」現地速報

次期APU“Carrizo”の概要が明らかに──「Future of Compute」現地速報

AMDがシンガポールで行っているイベントでは、次期APU「Carrizo」のほか、DirectX 12における性能向上やFreeSync対応4Kディスプレイにも言及している。