チップ面積・電力4分の1に 富士通、45ナノ向け新技術

» 2006年06月16日 17時25分 公開

[ITmedia]

富士通研究所と富士通は6月16日、45ナノメートル世代のロジックLSI向け低消費電力技術を開発したと発表した。現状の90ナノメートル世代と比べ、チップ面積と消費電力を約4分の1にできるという。

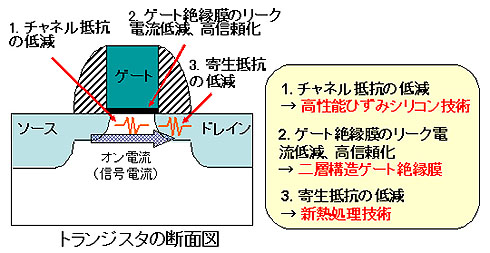

歪みシリコン技術によるチャネル抵抗の低減や、2層構造のゲート絶縁膜技術などで信号電流の増加とリーク電流の低減を図った。従来の45ナノ技術と比べ、同じ信号電流とリーク電流で電圧を1ボルトから0.85ボルトに低減でき、消費電力を30%低減可能だとしている。

新技術の適用で、現在のLSIと同等の処理を低消費電力で行ったり、同等の電力で処理を複雑化できる。デジタルAV機器の画像処理LSIや、マルチコア化したマイクロプロセッサなどへの適用を想定し、例えばワンセグ放送などのH.264コーデック処理LSIに使った場合、安価な携帯カメラでも高精細な映像を記録できる上、長時間の撮影も可能になるとしている。

詳細は、半導体の国際学会「Symposium on VLSI Technology」(米国ホノルル)で発表した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PRアイティメディアからのお知らせ

SpecialPR

あなたにおすすめの記事PR