東芝、IBM、AMD、世界最小の立体構造トランジスタSRAMセル開発

» 2008年12月18日 07時00分 公開

[ITmedia]

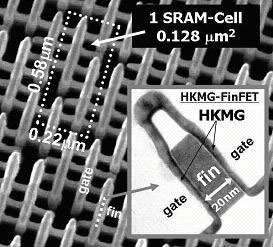

東芝と米IBM、米AMDは12月17日、セル面積が0.128平方マイクロメートルと、立体型としては世界最小のSRAMセルを開発し、動作を確認したと発表した。より小型で高速・低消費電力なプロセッサ開発につながるとしている。

フィン形状の立体構造電界効果トランジスタ(FinFET)と、高誘電率(High-k)ゲート絶縁膜、メタルゲートを採用し、これまで最小だった0.274平方マイクロメートルのセルより50%以上小型化した。

従来の平面トランジスタは、シリコンチャネル部分に不純物を注入することで小型化していたが、不純物は動作の安定性を損なう可能性があり、これが22ナノメートル世代以降で特に大きな問題なっているという。

不純物の注入が不要なFinFETなら、特性のばらつきを抑制しながらSRAMセルの小型化が可能で、22ナノメートル世代以降で平面型より優位としている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PRアイティメディアからのお知らせ

SpecialPR

あなたにおすすめの記事PR