Intelのさらなる“やらかし”と、Intelが主導するPCアーキテクチャの終わり:“PC”あるいは“Personal Computer”と呼ばれるもの、その変遷を辿る(2/3 ページ)

そのADTであるが、何しろもうADT Allianceそのものが残っていないからどんな技術を検討していたのかを正確に知ることは難しい。ただ、当時の記事などから、

- Latencyを下げること:Direct RDRAMの性能が出なかった直接的な理由は、その無茶苦茶に大きなLatencyにある。メモリアクセスをパイプライン化することである程度遮蔽は可能だが、連続アクセスはともかくランダムアクセスになるとLatencyの大きさが際立つことになった。そこでLatencyを下げる方策が必要とされた。

- 信号伝達特性の安定化:Direct RDRAMでもいろいろと苦労しただけに、安価な4層PCBでも安定した信号伝達が可能となる工夫が必要と考えられた。

という2つの要件が盛り込まれたのは間違いない。

まずLatencyであるが、Direct RDRAMのようにバス幅を狭める(64bit→16bit)と、その変換で余計に時間がかかるのは当然である。

この当時のIntel CPUは64bitのバス幅で信号を出しており、これを16bitに狭めたり、逆に16bitから64bitに広げるのは単にLatencyを増やすだけ。このためSDRAMやDDR-SDRAMと同じ、64bitのパラレルバス方式がLatency削減には必須と考えられたようだ。加えて、Strobelessへのチャレンジも考えられていた。

Strobeless、要するに「ストローブ信号が無い」の意味だが、そもそもストローブ信号とは?を先に説明しておく。ちょっと前回の図を見ていただくと、一番上にRAS#(Row Address Strobe)とCAS#(Column Address Strobe)という2本の信号があるのがお分かりかと思う。この2本の信号は、

- RAS#:この信号がLowになったタイミングで、アドレスバスにRowアドレスが出ている

- CAS#:この信号がLowになったタイミングで、アドレスバスにColumnアドレスが出ている

ことを示すものである。

ただこれメモリの側からすれば、まずRAS#なりCAS#なりの信号を監視して、それからアドレスバスの値を取り込むことになるので効率が悪い。これを省くことで、プロトコルのオーバーヘッドが削減できることを狙った模様だ。

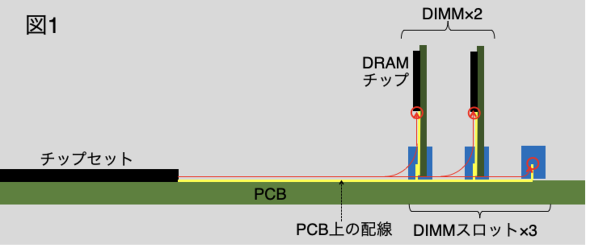

次いで信号の伝達特性改善だが、ADTではActive Terminationの実装を想定していた。図1は、いわゆるマザーボードのメモリバスの接続を横から眺めたものだ。

チップセットから、PCB上の配線を経由して、3つあるDIMMスロットに信号は分配される。現在はここに2枚のDIMMが装着されている形だ。

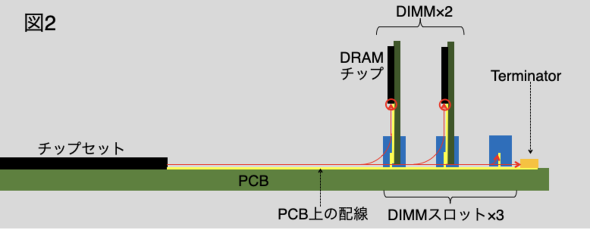

さて、この構図で信号(赤の矢印)がチップセットから送り出されると、赤丸のある場所で信号は行き止まりになる。信号の速度が遅いと後はそのまま減衰して終わりなのだが、信号の速度が速くなると、ここで減衰せずに反射してチップセットの方に信号が戻ってしまう。これは信号速度が高速になるほど深刻さを増し、安定した信号伝達の妨げになる。そこでDDR-SDRAMでは図2のようにPCB上の配線をDIMMスロットの先まで伸ばし、そこにTerminatorと呼ばれるものを実装した。

要するに抵抗であるが、ここに信号が到達すると、そのまま抵抗で信号が消滅するので反射しなくなる、というものだ。

これでDIMMスロットの空き分は解決できたが、DRAMチップの側の反射はなくならない。かといって、無条件にDRAMチップにTerminaorを入れたら、信号がDRAMチップに届く前に減衰してしまう。

そこで「チップがアクセスをしたいときはOff、休止状態の時にはOnになるTerminatorをDRAMチップ内に入れ込む」というアイデアが出てきた。これがActive Terminatorと呼ばれるものだ。この方式、DRAMベンダーからするとコストアップにつながるということで当初は難色を示していたが、最終的にDDR-II世代で導入が決まっている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR